| Annexe 12 | Extrait du manuel de référence de la carte<br>processeur dédiée au traitement du signal<br>DX 2100 | 16 pages |

|-----------|----------------------------------------------------------------------------------------------------|----------|

|           |                                                                                                    |          |

# CARTE PROCESSEUR DEDIEE AU TRAITEMENT DU SIGNAL ET AU CONTROLE/COMMANDE TEMPS REEL DX2100

Version PC

Extrait du manuel de Référence

# 1. INTRODUCTION

La carte DX2100 est la réponse au besoin en vitesse de calcul de plus en plus marqué, dans les domaines de l'automatique, de la robotique et du traitement du signal en temps réel.

Elle comble le créneau entre les réalisations câblées envahissantes et peu souples et les solutions programmées, plus flexibles mais plus lentes.

Cette solution permet de protéger les investissements du client sans rien céder en performance par rapport à des systèmes dédiés beaucoup plus onéreux.

Cette carte au format PC/XT/AT existe aussi dans une version Station Apollo. Le format Multibus I (Intel) est également disponible.

Grâce à sa structure en pipe-line, deux opérations (+ et \*) peuvent être exécutées dans le même cycle machine .

Pour un temps de cycle de 100ns on obtient une vitesse crête de 20 millions d'opérations par seconde.

L'utilisation simultanée de plusieurs cartes DX2100 communiquant entre elles grâce à un bus privé à 160 Mbits/seconde permet d'envisager des applications lourdes à faible coût.

Enfin une large gamme de modules et de cartes d'entrées/sorties est disponible afin de répondre à des applications très variées aussi bien en contrôle/commande de processus (asservissements, filtrage, calculs matriciels...), qu'en traitement du signal (FFT, convolution, corrélation, filtrage, génération de signaux...).

# 2. ARCHITECTURE MATERIELLE DE LA VERSION PC

Structurée autour de l'ADSP2100 d'Analog Devices et supportée par le bus PC, la carte DX2100 offre une structure lui permettant de répondre à une large gamme d'applications dans les domaines du contrôle/commande et du traitement du signal.

Son architecture de transfert sur 8 bits lui permet d'être compatible avec toutes les versions de compatibles PC,

et ceci quel que soit le langage de programmation utilise.

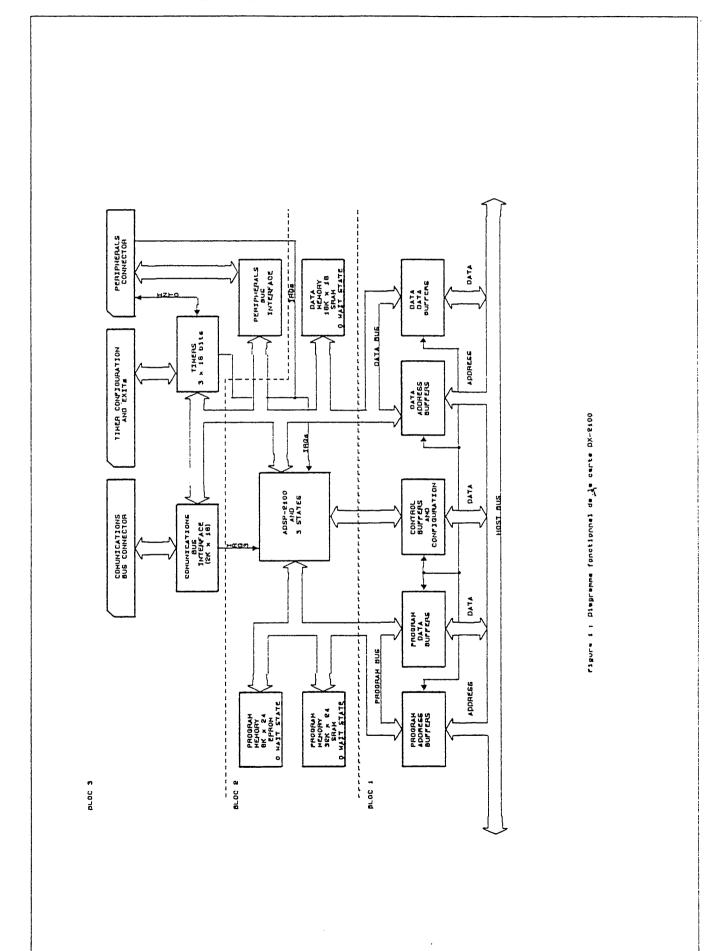

Le schéma de la <u>figure 1</u> (p.5) montre le diagramme fonctionnel de la carte DX2100.

On remarque trois parties bien distinctes sur ce diagramme :

- 1 Le bloc de communication vers l'HOTE.

- 2 Le noyau de la carte comprenant l'ADSP2100 et sa mémoire.

- 3 Le bloc de communication vers le monde extérieur.

#### 2.1 L'INTERFACE AVEC LE HOTE/PC

Dans tous les systèmes compatibles PC travaillant sous PC-DOS, l'espace mémoire maximal géré est de 640 K, par conséquent, à partir de l'adresse A000:0000HLa mémoire est disponible.

Dans l'ensemble de l'espace disponible dans la mémoire RAM, on distingue :

- la page \$B000 et les suivantes utilisées par les organes graphiques,

- la page \$F000 utilisée par la ROM système.

- des cartes multifonctions qui proposent des disques virtuels dans la page \$D000.

Pour la carte DX2100, la partie haute de la page \$D000 a été choisie afin d'effectuer les accès sur la mémoire du DSP suivant un champ continu de 32 K de 8 bits.

Une zone de 64 Ko est donc réservée lors de l'implémentation d'une carte DX2100 dans le PC.

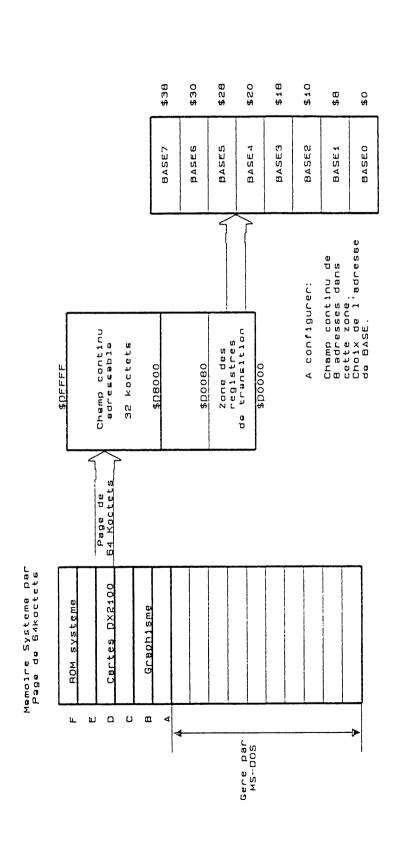

La <u>figure 2</u> (p.6) schématise la zone mémoire du PC occupée par la carte DX2100.

Figure 2 : Zone memoire du PC occupe@par les cartes DX-2100

On peut remarquer, sur cette figure, le champ 32 K octets continu adressable qui se situe dans la moitié haute de la page.

On verra ultérieurement que ce champ permet l'accès à la totalité de la mémoire du DSP.

On peut également observer que, dans la moitié inférieure de la page \$D000, un bloc de huit registres est utilisé à la commande de la carte DX2100.

En réalité, la carte nécessite 5 registres pour son fonctionnement. Il est possible de disposer, sur un même fond de panier un maximum de 8 cartes (16 dans des cas particuliers) chacune disposant d'une adresse de base différente (configurée modulo 8).

La <u>figure 3</u> (p.8) montre le rôle de chacune des 5 adresses utilisées pour assurer la communication entre l'HOTE et le DSP. On remarque dans ce tableau les registres suivants :

ADRESS low Register (BASE)

ADRESS high Register (BASE + 1)

Ces deux registres correspondent à l'adresse en cours dans l'espace programme du DSP respectivement pour les poids faibles (8 bits) et pour les poids forts (7 bits).

Ils sont lisibles depuis l'HOTE quand ce dernier détecte la présence d'un TRAP sur le DSP. Ce TRAP est détecté, soit par la lecture à partir de l'HOTE du STATUS Register ou par le déclénchement sur l'HOTE de l'interruption matérielle configurée sur la carte DSP.

Des exemples d'utilisations de ces registres pour la mise au point d'applications sont décrits au paragraphe III.

#### DMA Register (BASE+2)

D0 à D4 sont utilisés pour configurer l'aiguillage vers un des cinq champs mémoire 8 bits accessibles par l'HOTE, à savoir :

- poids faibles espace programme,

- poids moyens espace programme,

- poids forts espace programme,

- poids faibles espace données,

- poids forts espace données.

L'accès à des champs de mémoire va être réalisé suivant les diagrammes décrits sur les  $\frac{1}{1}$  (p.15, 16).

|            |        |                 | _          |            | ,                                        | 4                      |   |     |                                         | _                             |     | 1     | ٦                                      |      | 7      |

|------------|--------|-----------------|------------|------------|------------------------------------------|------------------------|---|-----|-----------------------------------------|-------------------------------|-----|-------|----------------------------------------|------|--------|

|            | 00     |                 |            | 0 -        | PAB                                      |                        |   | o   | Memoire<br>Programme<br>Poids<br>feible |                               | 0 - | IRGO  |                                        | 0 -  | TRAP   |

|            | 0.1    | OSP.            |            | 0 7        | 0SP.                                     |                        |   | 03  | Memoire<br>Programme<br>Poids<br>moyen  |                               | -   | IRO1  |                                        | . c  | 90     |

|            | D2<br> | COURS SUR LE    |            | 20         | PA10<br>SUR LE                           |                        |   | D2  | Mamoire<br>Programme<br>Poids           | A LE HOTE.                    | 20  | IROS  |                                        | - 05 | - UZ   |

| L Register | D3     | ST              | H Resister | £0         | PA12 PA11<br>DE L'INSTRUCTION EN COURS   | ae du osp.<br>Realster |   | 63  | Memoire<br>Donness<br>Poids<br>feible   | ES DU DSP PAR<br>UP Register. | £0  | IAG3  | L'ETAT DU DSP.<br>IUS Register.        | 60   | - CV   |

| : Adress   | D 4    | 7 PA44          | : Adress   | D 4        | 1 1                                      | A LA MEMOIRE           | 1 | 0 4 | Memoire<br>Donnees<br>Poids<br>fort     | ONS MATERIELLES<br>: INTERBUR | D 4 | PESET | VERIFICATION DE L'E<br>BASE+4 : STATUS | D 4  | - UZ   |

| BASE       | 50     | FAIBLE OE L'ADF | BASE+1     | 0.5        | FORT DE L'ADRESSE                        | ACCES A                |   | 2   | Gestion<br>du TOC                       | INTERRUPTIONS<br>BASE+3 :     | 50  | - UZ  | VERIFI<br>BASE+4                       | 50   | O<br>Z |

|            | 90 -   | PAG FA          |            | 90         | POIDS FC                                 |                        |   | 90  | HALT<br>du OSP,                         |                               | 90  |       |                                        | 90   | U      |

|            | 07     | 7-7-4           |            | <b>C</b> 0 | J. J |                        |   | 70  | Demanda<br>d'acces e<br>le memoire.     |                               | 20  | ç     |                                        | 60   | U      |

FIGURE 3 ; Role des edresses utilisees pour essurer le communicetion elgune 3 ; Role de la DSP.

D5 est utilisé pour la gestion du TOC (Time Out Control). De plus amples renseignements sur le fonctionnement du TOC sont décrits dans le paragraphe 3 (p.13).

D6 utilisé pour stopper le DSP.

D7 utilisé pour demander le bus du DSP afin d'accéder à sa mémoire. La lecture du STATUS REGISTER informe sur l'autorisation d'accès.

## INTERRUPT Register (BASE + 3)

Le ADSP2100 dispose de 4 interruptions entièrement masquables et configurables; le rôle des quatre premiers bits de ce registre est de déclencher ces interruptions depuis l'HOTE si elles ne sont pas masquées par le DSP.

Le bit 4 permet d'effectuer un RESET.

## STATUS Register (BASE + 4)

Le contrôle du transfert des données entre l'HOTE et la carte  ${\tt DX2100}$  s'effectue par ce registre qui permet :

- Une vérification de la réponse du DSP (D1) à la requête de l'HOTE qui lui demande l'accès à sa mémoire.

- Un contrôle de l'état du signal TRAP (D0) qui correspond à la demande d'interruption du DSP à l'HOTE.

Ce même signal TRAP est véhiculé (par configuration matérielle) vers une interruption de l'HOTE.

Une telle structure permet le travail en parallèle des deux processeurs. Quand l'un des deux a besoin de transférer des paramètres vers l'autre, il fixe une interruption qui peut être ou pas masquée par l'autre.

# 2.2 LE MICROPROCESSEUR ADSP2100 ET SA MEMOIRE

Les premières versions de l'ADSP2100 travaillaient avec un temps de cycle de 170 ns puis de 125 ns.

Les versions actuelles fonctionnent avec des temps de cycle de

100 ns : Carte DX2100-CL 80 ns : Carte DX2100-CM

La mémoire statique utilisée sur les cartes DX2100 (temps d'accès : 35 ns) ne suscite aucune contrainte et est accessible pour les 2 versions, avec "O Wait State".

Dans les différentes zones mémoires, on trouve :

- Un espace programme de 16K mots de 24 bits.

- Un espace coefficient de 16K mots de 16 bits, utilisables sous forme virgule flottante IEEE sous 24 bits.

- Dans la partie inférieure de l'espace programme, sont disposés en parallèle avec celui-ci, 8K mots de 24 bits de UV-PROM utilisables par configuration matérielle.

- Un espace données de 16K mots de 16 bits.

Dans cet espace, décrit <u>figure 4</u> (p. 11), sont disposés les champs suivants :

- \* espace utilisateur (13.75K X 16 bits)

- \* espace R.O.I (region of interest) : zone d'intérêt destinée à l'extension mémoire par pages de 1 K 16 bits et à la communication entre plusieurs cartes DX2100 (16 au maximum).

La gestion MMU (Memory Management Unit) peut gérer un maximum de 2<sup>16</sup> pages de 1K, ce qui permet d'obtenir un espace mémoire maximum de 65 Mmots.

L'extension mémoire est disponible sur une carte au format PC, DX2125-C, contenant 1 Mmot (100 ns de temps d'accès).

Un maximum de 4 cartes DX2125-C peuvent être implémentées dans un système. Cette zone R.O.I est disponible par le connecteur CON4.

\* espace périphériques de 256 mots de 16 bits permettant l'ensemble des accès vers les éléments d'entrée/sortie soit internes à la carte soit externes sous forme de modules ou de cartes additionnelles.

La <u>figure 5</u> (p.12) montre les adresses utilisées dans les éléments internes et celles utilisées par quelques modules.

L'ensemble de l'espace périphérique est disponible sur la carte par les connecteurs CON1 et CON2.

|                                                                                                                                                  | LOGADEX                  | TOOLOOSE                                        | DAZIOO.PC |                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------|-----------|--------------------------------------------|

| <ul> <li>4-Zone peripheriques 512 x 16 bits</li> <li>4-Zone TéServée</li> <li>4-Zone d'interet ik x 16 bits</li> <li>7-Communications</li> </ul> | <b>D</b>                 | , Espace donnaes disponibla<br>13.75k X 16 bits |           | o p                                        |

|                                                                                                                                                  |                          |                                                 |           | Figure 4: Diagramme fonctionnel du partage |

| \$3FFF 16K<br>\$3E00<br>\$3C00                                                                                                                   | \$3800  <br>\$2FFF   12K | #1FFF 8K                                        | \$0FFF 4K | 0 0000\$                                   |

| \$3FFE<br>\$3FFD | CNTL TMB         |                                   |

|------------------|------------------|-----------------------------------|

| SSFFD            |                  | Timeur sur la carte mere          |

| C 17 to 6        | TIMER1           |                                   |

| 7                | ТІМЕВО           | /                                 |

| <b>\$</b> 3FFB   | CNTL, IBQ        |                                   |

| \$3FFA           | CNTI, IBO        | couplees au Timeur. Gestion de BA |

| \$3FF9           | QUT2105 1        | <i>,</i>                          |

| \$3FF8           | IN2105 1         |                                   |

| <b>\$</b> 3FF7   | DXM2106 1        |                                   |

| \$3FF6           | QUT2105 2        | 000                               |

| \$3FF5           | 0 5010NT         |                                   |

| \$3FF4           |                  |                                   |

| \$3FF3           | AMERICA &        |                                   |

| \$3FF2           |                  | <br>T                             |

| \$3FF1           |                  |                                   |

| \$3FF0           |                  | 20ne reservee aux peripheriques   |

|                  |                  |                                   |

| . 4              | ,                | <u> 77</u>                        |

|                  |                  |                                   |

| \$3EF2           | DXC2125          |                                   |

| \$3EF1           | DXC2125          |                                   |

| \$3EF0           | DXM2101. DXC2125 |                                   |

|                  |                  |                                   |

# 3. EXEMPLES D'UTILISATION DES REGISTRES

## 3.1 ACCES A L'ESPACE MEMOIRE

Quand l'HOTE souhaite accéder au bus du DSP il va effectuer les étapes suivantes :

- positionnement du DMA Register avec la demande d'accès au bus et le champ mémoire demandé.

Si par exemple il souhaite accéder au poids moyen de l'espace programme, la valeur du DMA Register sera :

D7 D0 0 1 1 1 1 1 0 1 soit 7DH

Soit positionnement des bits D7 et D1 à zéro, ce qui correspond respectivement à la demande du bus et à l'ouverture de la "porte" correspondant au champ mémoire 8 bits souhaité (voir figure 3, p.8).

Les bits restants D0 et D2 à D4 positionés à 1 indiquent que les "portes" des champs mémoire restants sont fermées et par conséquent inaccessibles.

Si plusieurs "portes" sont ouvertes, l'accès est possible sur plusieurs champs à la fois, ce qui est un avantage pour l'écriture de données, néanmoins il faut être prudent dans les phases de lecture de données.

- L'accès au bus du DSP par l'HOTE est conditionné à la confirmation du DSP. Ainsi les "portes" vers les champs mémoire ne sont pas ouvertes sans que le DSP l'autorise.

L'HOTE doit venir tester la disponibilité du BUS avant de faire ses accès par test du STATUS Register, qui se présente de la façon suivante :

DO : TRAP. Actif à l'état haut.

D1 : Disponibilité du bus. Disponible à l'état bas.

Les bits restants étant réservés.

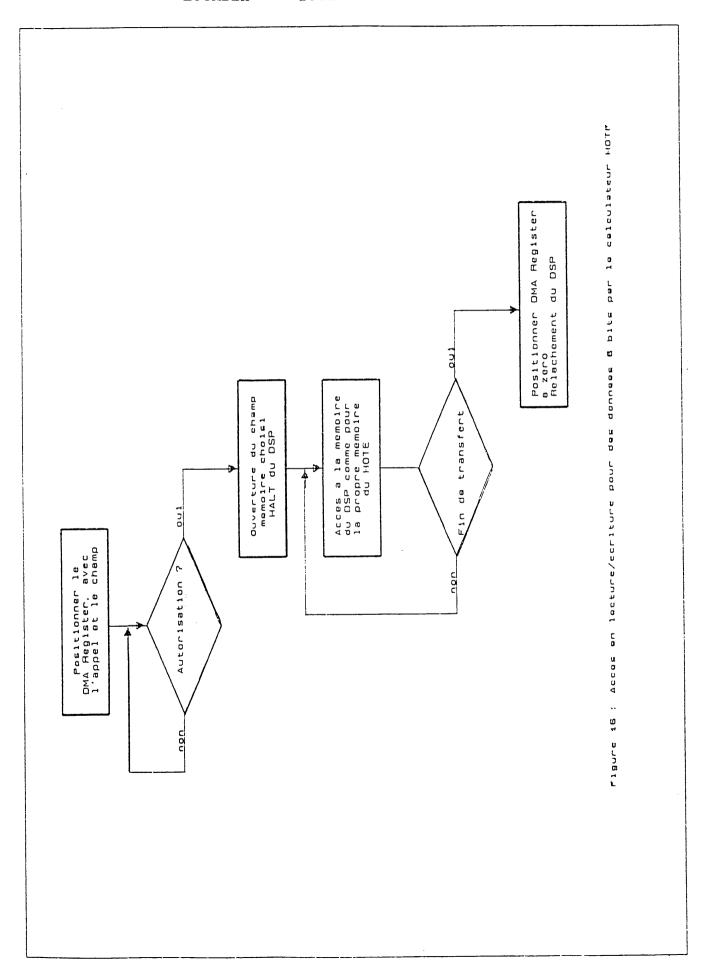

L'organigrammme de la <u>figure 16</u> (p.15) montre les accès en lecture ou en écriture de la mémoire du DSP, pour une donnée de 8 bits.

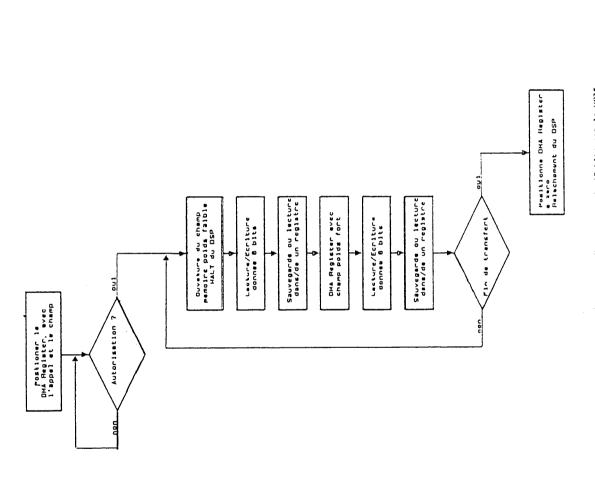

L'organigramme de la <u>figure 17</u> (p. 16) montre les accès en lecture ou en écriture de la mémoire du DSP, pour une donnée de 16 bits.

On peut remarquer sur ces organigrammes que :

- l'accès à une donnée 8 bits nécessite un minimum de quatre instructions dont trois de contrôle et une effective.

On peut constater qu'il est plus intéressant de transférer des champs continus de données que des données ponctuelles.

- l'accès à une donnée de 16 bits nécessite un minimum de neuf instructions dont cinq de contrôle, deux effectives.

Au même titre que les données 8 bits, il est préférable d'accéder à des champs continus que d'accéder à des données ponctuelles.

# 3.2 PRISE DE CONTROLE DU DSP PAR L'HOTE

Les échanges d'informations entre l'HOTE et le DSP sont conditionnés par les signaux suivants :

- <u>RESET</u>: Initialisation du DSP, qui peut être effectuée de trois façons différentes:

- . Reset du calculateur HOTE qui s'effectue à la mise sous tension de l'ensemble de l'équipement,

- . Reset réalisé par le bouton poussoir situé en face arrière,

- . Reset logiciel transmis par l'HOTE via le bit D4 de L'INTER-RUP Register (BASE + 3).

Le Reset est actif à l'état bas.

- <u>HALT</u>: Ce signal transmis par le bit D6 du DMA Register arrête le fonctionnement du DSP. Ce dernier termine le cycle en cours et s'arrête. Le relâchement du HALT fait repartir le DSP. Ce signal est souvent utilisé en association avec le signal TRAP.

Le HALT est provoqué par l'HOTE en positionnant le bit D6 du DMA Register (BASE + 2).

- Il est actif à l'état bas quand JP17 est mis et JP16 oté.

- Il est actif à l'état haut quand JP17 est oté et JP16 mis.

Le positionnement de JP16 et JP17 est fonction du mode de fonctionnement, soit en mode "résident" ou en mode "télécharge". Se référer au paragraphe de configuration pour de plus amples renseignements sur ces "straps".

Tigure 17 i boces en leotura/spritture d'une donnes de 18 bits per le HUIG.

# 4. CONFIGURATIONS

## 4.1 CONFIGURATION DE L'ADRESSE DE BASE

L'adresse de BASE de la carte vue par l'HOTE va se situer dans la page \$D0000 aux adresses déterminées par le positionement de SW2 suivant le tableau ci-dessous :

SW2-1 SW2-2 SW2-3 SW2-4 SW2-5 SW2-6 SW2-7 SW2-8 ADRESSE

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | OH  |

|---|---|---|---|---|---|---|---|-----|

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 8H  |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 10H |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 18H |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 20H |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 28H |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 30H |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 38H |

1 = ON = FERME 0 = OFF = OUVERT

# 4.2 CONFIGURATION DES 8 PREMIERS KMOTS DE LA MEMOIRE PROGRAMME

Pour pouvoir utiliser les 8 Kmots de mémoire UV-PROM il est nécessaire de configurer SW4 et SW6.

SW4 mis et SW6 oté : mémoire RAM validée.

SW4 oté et SW6 mis : mémoire UV-PROM validée.

Les deux otés : pas de mémoire accessible dans les 8 Kmots d'adresse base.

Les deux mis : interdit.

## 4.3 CONFIGURATION DE LA MEMOIRE DONNEES

L'espace R.O.I. est validé ou pas en fonction de SW5.

SW5 mis : R.O.I validé et accessible sur CON4. Aux mêmes adresses, la mémoire RAM sur la carte, est inhibée.

SW5 oté : R.O.I invalidé et mémoire RAM sur la carte validée.