| LES RAPPORTS DES JURYS DES CONCOURS SONT ÉTABLIS SOUS I<br>RESPONSABILITÉ DES PRÉSIDENTS DE JURY | ΔA |

|--------------------------------------------------------------------------------------------------|----|

|                                                                                                  |    |

|                                                                                                  |    |

|                                                                                                  |    |

|                                                                                                  |    |

# MODALITÉS DU CONCOURS DE L'AGRÉGATION INTERNE

# ANNEXE A L'ARRETE DU 12 SEPTEMBRE 1988 FIXANT LES MODALITÉS DES CONCOURS DE L'AGRÉGATION

EPREUVES DU CONCOURS INTERNE DE L'AGREGATION

#### Section Génie électrique

#### A. - Épreuves écrites d'admissibilité

1° Première épreuve : Durée maximale : 8 heures. Coefficient : 1.

L'épreuve, qui prend appui sur un système industriel défini par une documentation technique s'organise en deux parties :

- La première permet d'évaluer les capacités du candidat à utiliser ses connaissances scientifiques et techniques pour expliciter ou valider les solutions retenues;

- La seconde permet d'évaluer les capacités du candidat à utiliser le support proposé pour élaborer un exercice permettant l'évaluation des connaissances et méthodes acquises par les élèves.

Le candidat doit situer l'exercice dans un processus d'apprentissage et par rapport aux autres enseignements scientifiques ou techniques qui lui sont associés.

2° Deuxième épreuve : Durée maximale : 6 heures. Coefficient : 1.

L'épreuve porte sur l'étude d'un problème d'automatisation. Elle permet d'évaluer les capacités du candidat :

- A mobiliser, ses connaissances en automatique et en informatique industrielle pour analyser et résoudre un problème d'automatisation;

- A proposer, pour certains points clés mis en évidence lors de l'étude, la ressource méthodologique et les techniques pédagogiques nécessaires à l'enseignement à un niveau de formation déterminé.

#### B. - Epreuves orales d'admission

#### 1° Première épreuve : Durée : 1 heure. Coefficient 1.

L'épreuve consiste en la présentation et la soutenance par le candidat d'un dossier original relatif à un projet qu'il a conduit dans le cadre de la discipline dans laquelle il enseigne.

Le thème du projet est pris dans les programmes des enseignements technologiques de la spécialité donnés dans les classes terminales de lycée ou dans les classes post-baccalauréat.

Le projet doit mettre en valeur :

- d'une part la dimension technologique du thème dans ses composantes scientifiques, techniques et aussi économiques, sociales et humaines;

- d'autre part les aspects pédagogiques en relation avec le niveau d'enseignement retenu.

Le candidat dispose de trente minutes pour présenter :

- les raisons qui l'ont conduit au choix du thème ;

- les réalisations (documents, matériels. logiciels....) relatives aux aspects techniques et pédagogiques du projet ;

- les objectifs pédagogiques retenus. leur opérationnalisation, notamment les modes et critères d'évaluation retenus ;

- les documents d'enseignement établis ;

Le jury, au cours de l'entretien de trente minutes qui suit l'exposé, peut :

- faire approfondir certains points du projet ;

- demander des précisions sur les solutions techniques adoptées ;

- faire expliciter certains aspects de la démarche pédagogique.

#### Le jury apprécie :

- la valeur industrielle, technique et économique du thème retenu ;

- la qualité du travail effectué ;

- les connaissances scientifiques et techniques du candidat ;

- la maîtrise de la didactique de la discipline, des méthodes et moyens d'enseignement ;

- la connaissance de l'environnement du système technique support du thème ;

- les qualités d'expression et de communication du candidat.

#### 2° Deuxième épreuve : Durée maximale : 8 heures. Coefficient 1.

Cette épreuve consiste à exploiter des documents techniques et pédagogiques relatifs à une séquence de « travaux pratiques » ou à une séquence à caractère expérimental, élément d'un processus d'apprentissage.

Elle permet d'évaluer les capacités du candidat à :

- proposer et justifier les principes, méthodes et modes opératoires à mettre en œuvre et à dégager les concepts auxquels ils se rattachent :

- réaliser, pour tout ou partie, selon la durée impartie, l'activité prévue.

Le programme du concours est défini par référence aux programmes des B.T.S. et D.U.T. de la spécialité.

N.B. – Afin de permettre au candidat de composer dans les disciplines correspondant à son enseignement, il choisira de traiter, pour l'ensemble des épreuves du concours, soit la dominante Electrotechnique soit la dominante Electronique.

### **AGREGATION**

## **SESSION 2003**

## **CONCOURS INTERNE**

**Section: GENIE ELECTRIQUE**

Option A: ELECTRONIQUE ET INFORMATIQUE INDUSTRIELLE

# ÉTUDE D'UN SYSTEME INDUSTRIEL

DUREE: 8 HEURES, COEFFICIENT: 1

Aucun document n'est autorisé.

Calculatrice autorisée (conformément à la circulaire n° 99-186 du 16 novembre 1999)

# Réseau d'alerte des pompiers

### Ce sujet comporte 5 cahiers distincts :

| Dossier technique de présentation     | (19 pages) |

|---------------------------------------|------------|

| Texte du sujet avec le questionnement | (13 pages) |

| Dossier technique - schémas -         | (12 pages) |

| Documents constructeurs               | (46 pages) |

| Documents réponses                    | (14 pages) |

#### Ce sujet comporte huit parties indépendantes :

| Partie 1 : Protocole de communication du réseau,      | <b>O</b> BLIGATOIRE |

|-------------------------------------------------------|---------------------|

| Partie 2: Programmation des trames au format MPT1327, | Au choix            |

| Partie 3 : Conception d'une séquence pédagogique,     | <b>O</b> BLIGATOIRE |

| Partie 4: Gestion (FP1).                              | <b>O</b> BLIGATOIRE |

| Partie 5 : Process audio (FP2)                        | <b>O</b> BLIGATOIRE |

| Partie 6 : Encodage / Décodage (FP3)                  | <b>O</b> BLIGATOIRE |

| Partie 7 : Interface clavier,                         | Au choix            |

| Partie 8 : Emetteur récepteur FM1000.                 | Au choix            |

Le candidat traitera obligatoirement les parties 1, 3, 4, 5 et 6 **et** l'une des parties au choix : 2, 7 ou 8. Le candidat doit faire preuve de sa compréhension de parties complètes du sujet, tant au niveau théorique qu'au niveau de son application pédagogique.

Une lecture préalable et complète du sujet est indispensable.

Les candidats sont invités à numéroter chaque page de leur copie et à indiquer clairement le numéro de la question traitée.

Les candidats sont priés de rédiger les différentes parties du problème sur feuilles séparées et clairement repérées. Chaque question est identifiée par une police *italique* et repérées par un numéro.

Il leur est rappelé qu'ils doivent utiliser les notations propres au sujet, présenter clairement les calculs et dégager ou encadrer tous les résultats.

Tout résultat incorrectement exprimé ne sera pas pris en compte. En outre les correcteurs leur sauront gré d'écrire lisiblement et de soigner la qualité de leur copie.

Il sera tenu compote de la qualité de rédaction, en particulier pour les réponses aux questions ne nécessitant pas de calcul. Le correcteur attend des phrases complètes respectant la syntaxe de la langue française.

Pour la présentation des applications numériques, il est rappelé que lors du passage d'une forme littérale à son application numérique, il est recommandé aux candidats de procéder comme suit :

- après avoir rappelé la relation littérale, chaque grandeur est remplacée par sa valeur numérique en respectant la position qu'elle avait dans la relation puis le résultat numérique est donné sans calculs intermédiaires et sans omettre son unité.

Si le texte du sujet, de ses questions ou de ses annexes, vous conduit à formuler une ou plusieurs hypothèses, il vous est demandé de la (ou les) mentionner explicitement dans votre copie.

# Dossier technique Le réseau d'alerte des pompiers

#### 1.1 DESCRIPTION DU RESEAU D'ALERTE DES POMPIERS

La coordination des moyens techniques des secours nécessite la présence d'un système de communication hautement sécurisé indépendant des moyens de communication utilisés par la population à laquelle il est destiné. Ce système de communication est appelé *Réseau d'Alerte des Pompiers*. Il a été mis au point par *Systel*, une société de Charente Maritime.

Le réseau d'alerte des pompiers est un système de communication radio maillé sécurisé couvrant un département. Ce système de communication est indépendant des autres systèmes de communication.

Un réseau d'alerte est placé sous la responsabilité d'un Centre de Traitement d'Alerte (CTA).

#### 1.2 COMPOSITION DU RESEAU D'ALERTE

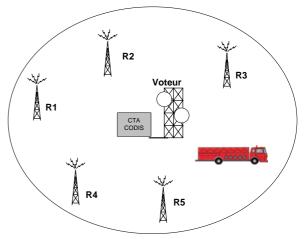

Le réseau d'alerte est composé de relais radio situés géographiquement de façon à couvrir le département dont est responsable le **C**entre de **T**raitement d'**A**lerte (CTA).

Suivant le relief, le nombre de relais varie entre trois et cinquante.

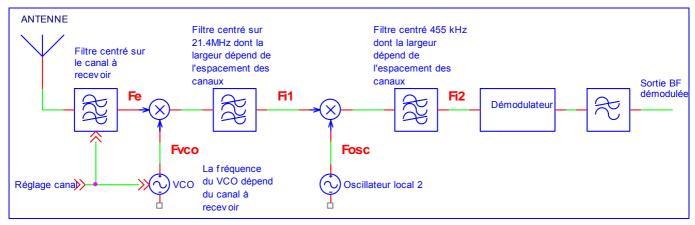

Le réseau fonctionne en mode simplex multiplexé pouvant gérer plusieurs canaux de communication à raison d'un couple d'émetteur et récepteur par canal.

Le département couvert par un réseau d'alerte est découpé en plusieurs zones opérationnelles. Chaque zone opérationnelle utilise des fréquences particulières dites canaux de communication.

Les canaux utilisés (liste non limitative) sont :

- Le canal opérationnel. Ce canal est utilisé pour transmettre les informations concernant les interventions avec les hommes sur le terrain.

- Le canal tactique. Ce canal est utilisé pour des plans d'interventions particuliers (plan ORSEC, plan POLMAR, ...).

- Le canal de commandement. Ce canal est utilisé pour établir les communications entre les autorités.

- Le canal SAMU.

- Le canal lien avec les autres départements,

- ...

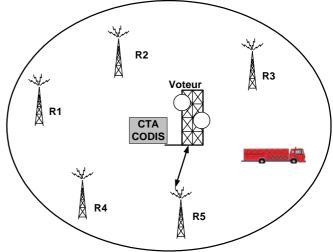

Figure 2.1 : Composition d'un réseau d'alerte sur un département

#### 1.3 FONCTIONNEMENT DU RESEAU D'ALERTE

Le réseau d'alerte fonctionne de la façon suivante :

- un appel vers le 18 aboutit au Centre Technique d'Alerte (CTA). Ce centre met l'auteur de l'appel en communication avec la caserne de pompiers la plus proche ayant des hommes et du matériel opérationnels.

- un suivi d'intervention (étapes de l'intervention) est alors déclenché par le personnel de la caserne. Ce suivi s'effectue sur deux niveaux : à la caserne et avec les pompiers envoyés sur le terrain.

Actuellement environs 30 départements et SAMU sont équipés de ce système de communication.

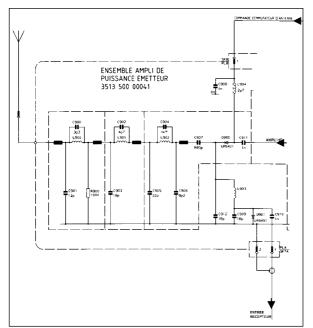

#### 1.4 COMPOSITION D'UN RELAIS

Un relais est un système radio informatisé à très haute fiabilité. Il se compose de 1..n équipements affectés chacun à un canal de communication particulier. Ces équipements sont montés en rack (RacER) ou en boite (BoxER).

Chaque relais est muni d'un identificateur unique mémorisé dans la mémoire de la carte VTXCOM.

#### 1.4.1 COMPOSITION D'UN EQUIPEMENT

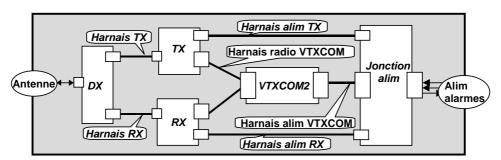

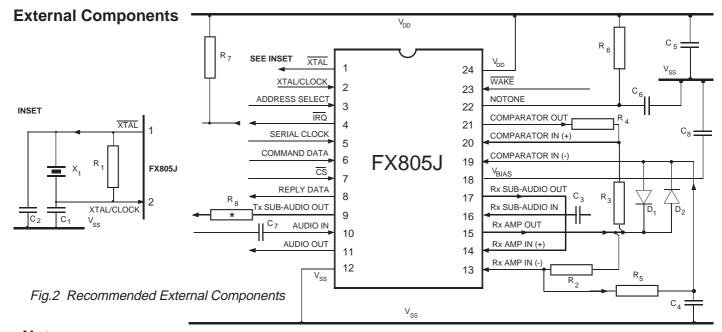

Figure 2.2: Composition d'un équipement de communication (station BoxER, doc SYSTEL).

#### Chaque équipement comporte :

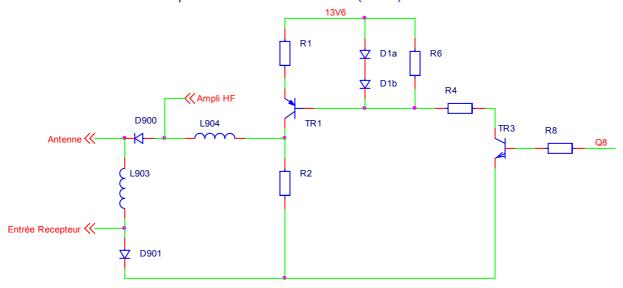

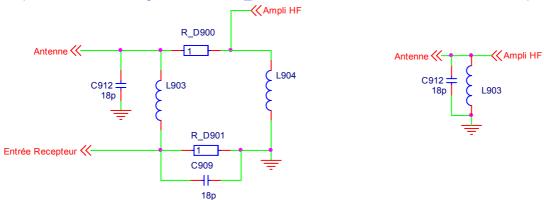

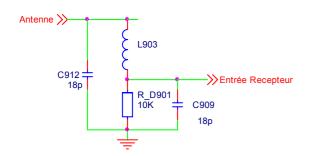

- Un équipement radio piloté par le système embarqué comportant :

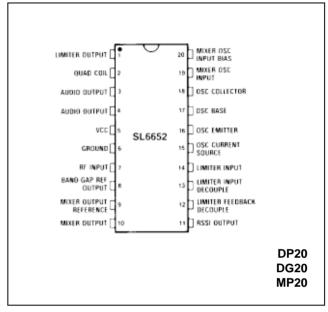

- Un récepteur radio FM1000 SE0 dans la bande des 80 Mhz.

- Un émetteur radio FM1000 SE0 dans la même bande possédant une puissance nominale de 15 à 80 watts suivant les équipements. Cette puissance est modulable. Emetteur et récepteur peuvent fonctionner simultanément (sur des canaux différents).

- Un système embarqué VTXCOM pilotant l'émetteur et le récepteur.

- Un système d'alimentation qui est fonction de la nature du terrain (certains relais sont inaccessibles 6 mois par an).

- Un duplexeur 6 cavités.

- Un système de liaison (optionnel) interconnectant les cartes VTXCOM situées dans le même relais.

- Un système de liaison (optionnel) interconnectant les cartes VTXCOM avec les cartes VTXCOM situées sur d'autres lieux géographiques. Le mode de liaison peut utiliser des lignes spécialisées, des modems sur réseau RTC, des faisceaux hertzien, des émetteurs / récepteurs dédiés. Le mode de communication est transparent pour la carte VTXCOM.

# 2 FONCTIONNEMENT D'UN CANAL OPERATIONNEL

Le canal opérationnel est utilisé pour transmettre les informations concernant les interventions avec les hommes sur le terrain. Chaque pompier est équipé d'un poste mobile fonctionnant en mode simplex (alternat). Ce mode implique de la part des hommes sur le terrain une utilisation du mobile de façon concise et précise. En plus de la phonie et pour minimiser l'occupation du canal, une grande partie des informations est transmise sous la forme de données constituées de trames CCIR et FSK 1382. Les données portées par ces trames correspondent à des situations préétablies dans différents domaines d'intervention. Ces informations sont émises à l'aide de touches placées sur le poste mobile. A tout moment, chaque mobile doit être dans le domaine de couverture d'un ou plusieurs relais.

#### Communication CTA vers mobile:

Pour entrer en contact avec un pompier sur le terrain, le personnel au CTA envoie une trame identifiant le mobile vers le relais utilisé lors de la dernière communication avec ce dernier. Cette trame est reçue par le récepteur du relais, après décodage par la carte VTXCOM; l'information qu'elle contient est ensuite réémise par le poste émetteur du relais vers le mobile.

#### Communication mobile vers CTA:

Toute communication entre le mobile et le CTA passe par une étape préalable d'élection du relais le plus approprié.

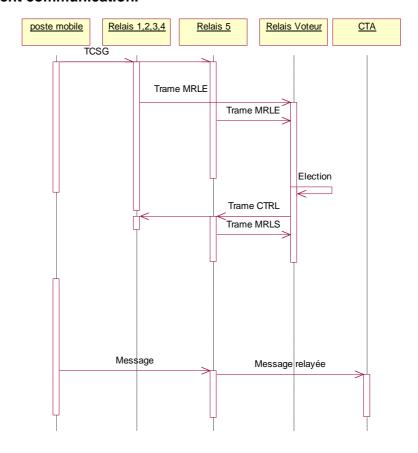

#### 2.1 ELECTION D'UN RELAIS

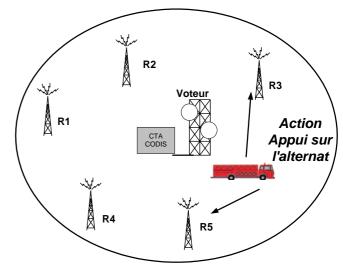

#### 2.1.1 PHASE 1: PUBLICATION

Pour entrer en contact avec le CTA, le pompier actionne une touche sur son mobile (touche pour la phonie ou touche encodant une situation préétablie). Celui-ci module la porteuse HF par un signal *TCSG* (voir document technique paragraphe mode auto ou mode contrôlé / inscription et élection).

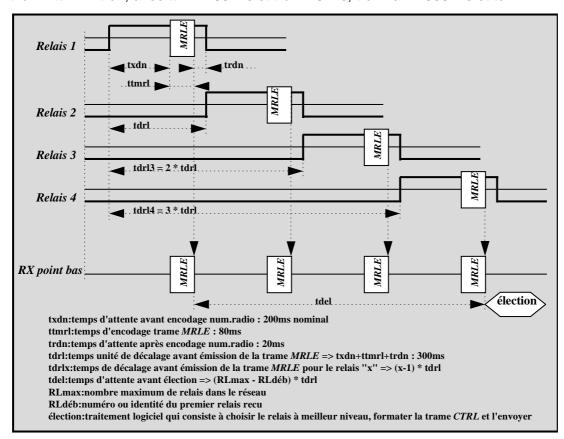

Figure 2.1: Election d'un relais : phase 1.

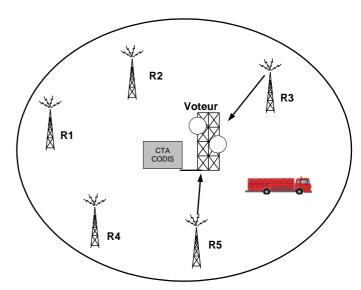

#### 2.1.2 PHASE 2: INCRIPTION

Les relais à portée du mobile mesurent l'intensité du champ reçu, puis encodent le niveau du champ ainsi que le numéro du relais dans une trame de type *MRLE*. A la disparition de la porteuse émise par le poste mobile, cette trame est transmise par les relais avec un décalage temporel fonction du numéro du relais vers le relais bureau de vote.

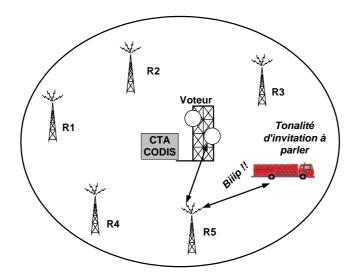

Figure 2.2: Election d'un relais: phase 2.

#### 2.1.3 Phase 3: Election et publication des resultats

La carte VTXCOM du relais *voteur* choisit le relais assurant la meilleure communication et émet une trame *CTRL* spécifiant le relais élu. A la réception de cette trame, le relais élu est activé et envoie un accusé de réception à l'aide d'une trame *MRLS*, les autres relais se mettent en attente d'une nouvelle communication.

Figure 2.3: Election d'un relais: phase 3.

#### 2.1.4 Phase 4: ETABLISSEMENT DE LA COMMUNICATION ENTRE LE MOBILE ET LE RELAIS

La communication entre le poste mobile passe alors par le relais élu.

Figure 2.4: Election d'un relais: phase 4

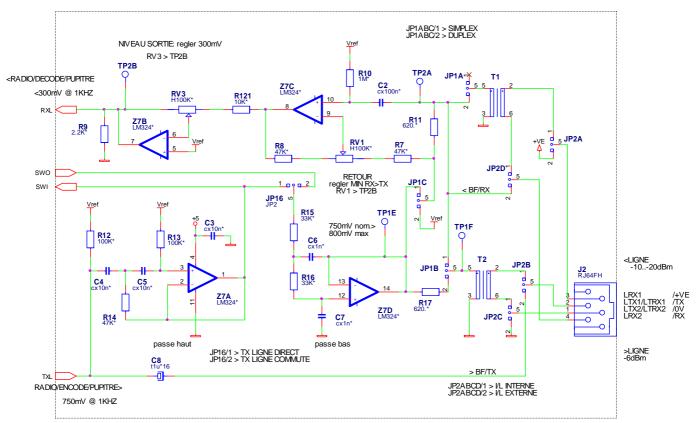

# 3 LES STATIONS RACER ET BOXER

Ce sont deux produits similaires :

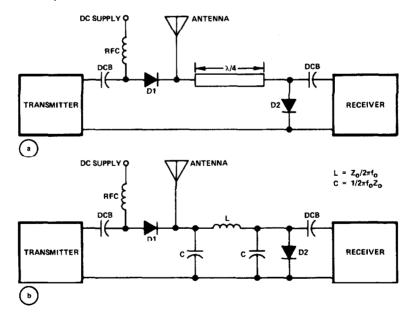

Une station BoxER (Boîtier Emetteur/Récepteur) se présente dans une boîte métallique et intègre la carte VTXCOM, un émetteur/récepteur (station simplex) ou un émetteur et un récepteur indépendant (station duplex réémettrice) et dans ce cas un duplexeur. (Voir schéma de d'interconnexion *Figure 2.1 page 9*).

Une station RacER (Rack Emetteur/Récepteur) se présente dans un tiroir rack 19" sauf qu'elle ne dispose pas de duplexeur, même dans le cas d'une station duplex. Dans ce cas, le duplexeur est reporté dans l'armoire ou directement au pied du mat d'antenne.

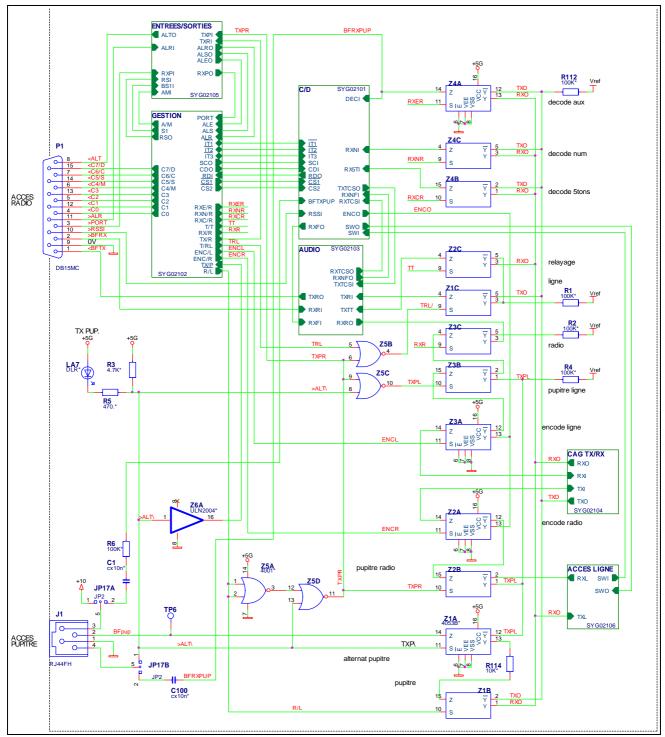

#### 3.1 LA CARTE VTXCOM

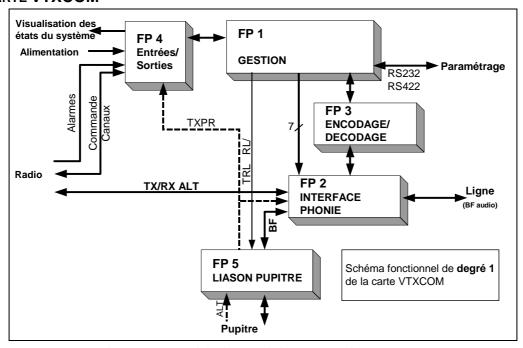

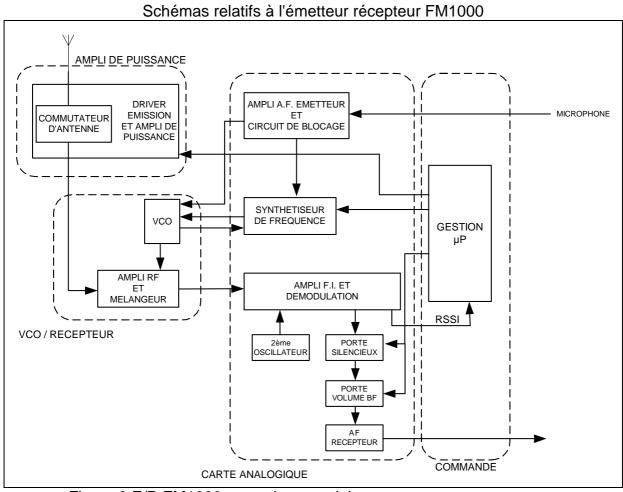

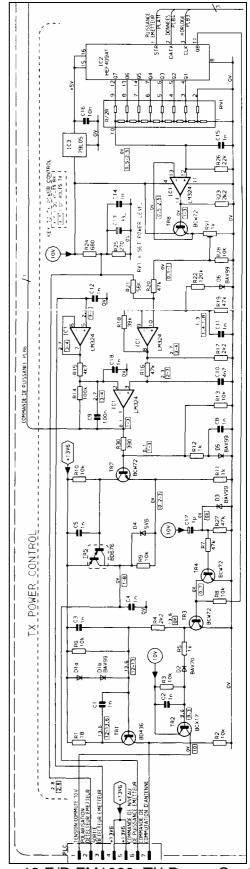

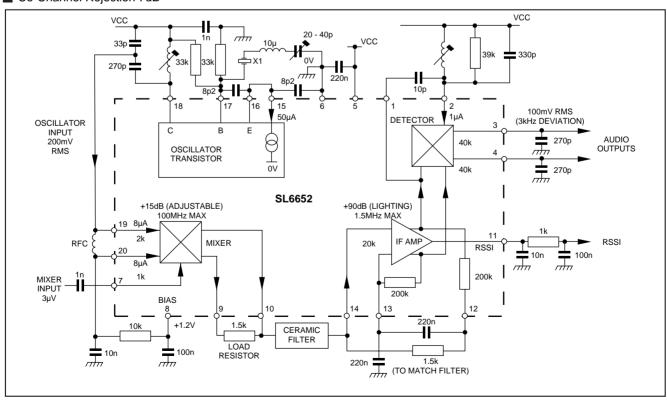

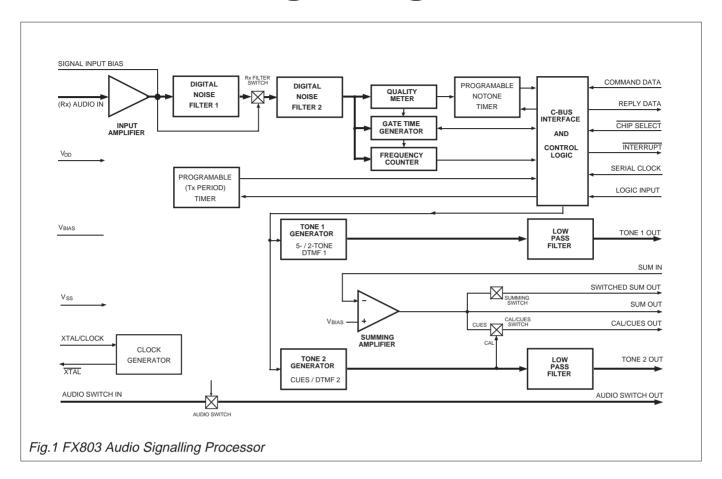

Figure 3.1 Schéma fonctionnel de degré 1 de la carte VTXCOM

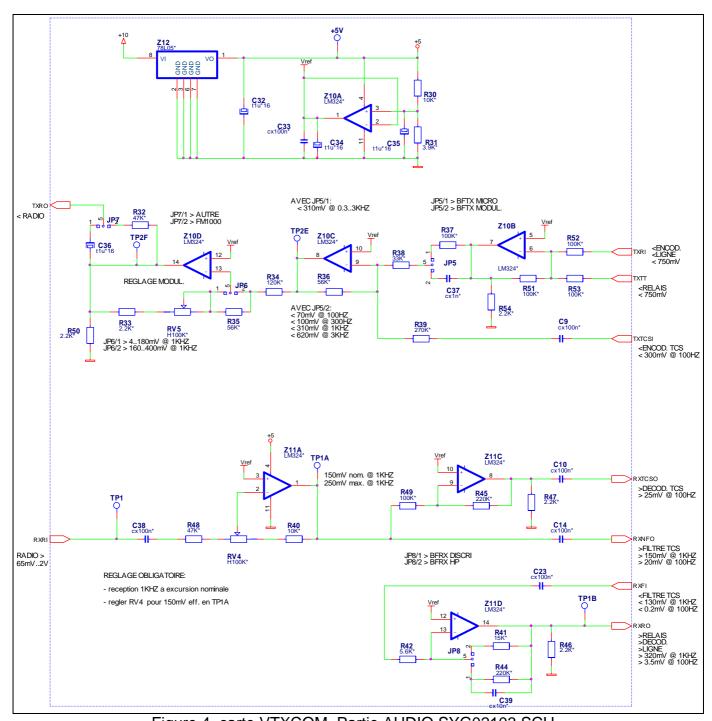

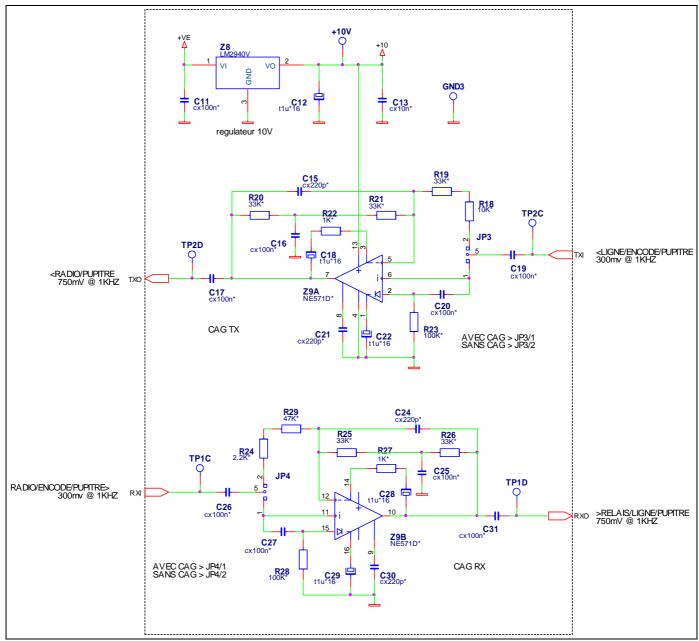

Les schémas structurels de la carte VTXCOM se trouvent page 2 à 8 du dossier "Schémas".

**Attention :** Le découpage hiérarchique des schémas par la société SYSTEL ne correspond pas exactement au découpage fonctionnel décrit ici. Le découpage adopté par SYSTEL est plutôt orienté "composants apparentés" que par fonction.

La carte VTXCOM se compose de 5 fonctions principales :

#### 3.1.1 FP1 GESTION

Elle permet la gestion logicielle des différentes fonctionnalités de la carte :

- Gestion et relayage des trames FFSK, TCS et 5 Tons ;

- Election d'un relais ;

- Gestion du relayage audio ;

- Paramétrage distant ou local.

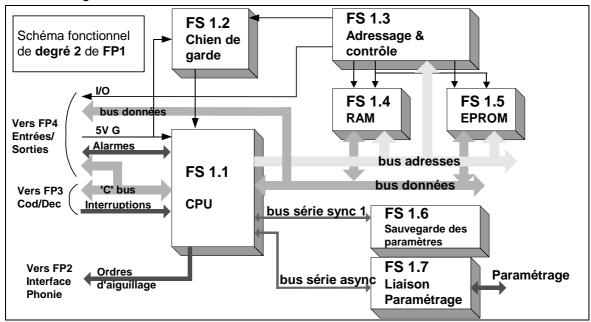

Figure 3.2 Schéma fonctionnel de degré 2 de FP1.

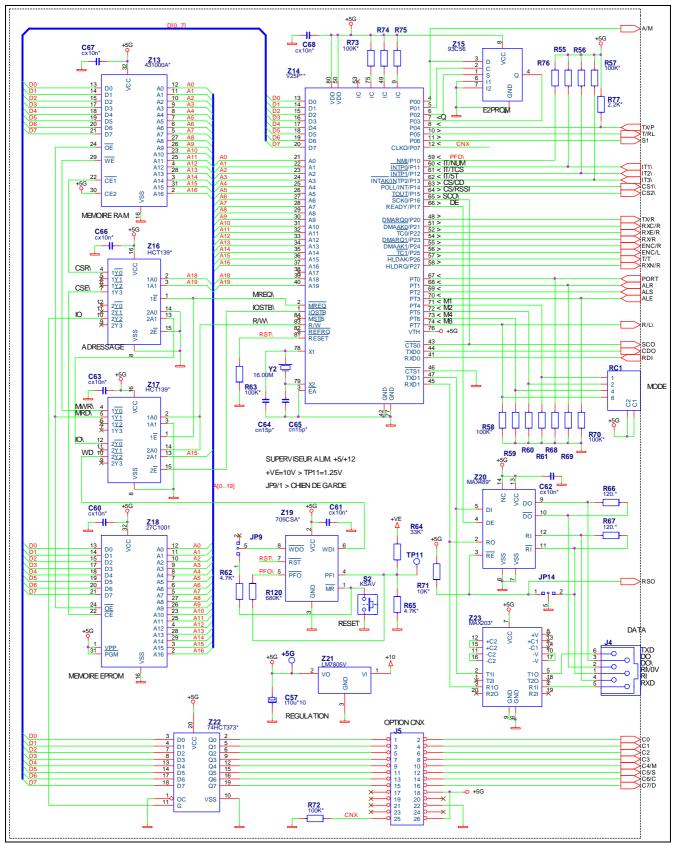

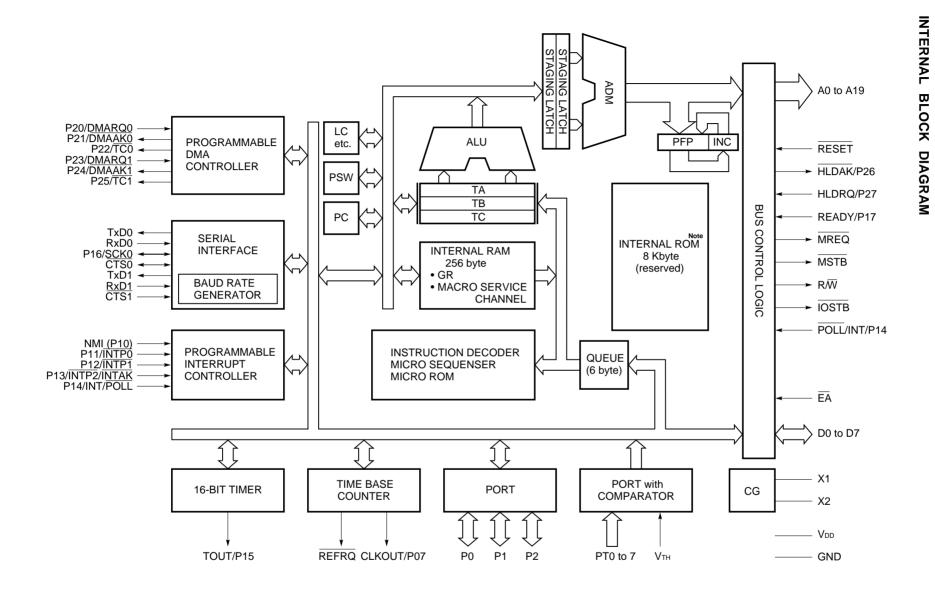

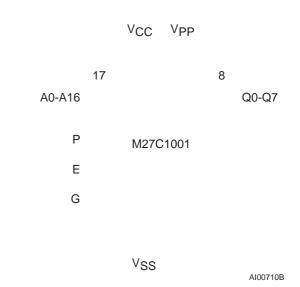

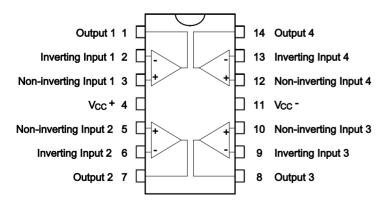

#### 3.1.1.1 FS 1.1 CPU

Elle se compose d'un microcontrôleur 16bits NEC: le V25+ (voir documentation constructeur).

Elle fonctionne avec un chien de garde (FS 1.3), une mémoire programme en EPROM (FS 1.5), une mémoire statique pour les données (FS 1.4) associés à un décodage d'adresse (FS 1.3).

Elle pilote l'aiguillage des signaux audiofréquence de **FP2** via 8 signaux logiques de commande issus de ses ports I/O (voir description des signaux au §3.1.2).

Elle dialogue avec les codeurs et décodeurs (**FP3**) via un bus série synchrone appelé **"C" bus** et 4 signaux d'interruption.

Elle dialogue avec FP4 par: des bits de ports en sortie destinés à relayer des états à visualiser, des bits de ports en entrée pour prendre en compte des alarmes et des états à surveiller, le "C" bus pour piloter un CAN et le bus de données pour piloter des périphériques optionnels. Tous ces signaux sont décrits au § 3.1.4.

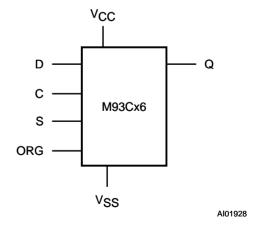

#### 3.1.1.2 FS 1.6 Sauvegarde des paramètres

Les paramètres de la station (canal, type, adresse ...) sont mémorisés dans une EEPROM série synchrone.

#### 3.1.1.3 FS 1.7 Liaison paramétrage

La carte VTXCOM peut être paramétrée par un PC ou un PDP, via une liaison série asynchrone de type RS232 ou RS422.

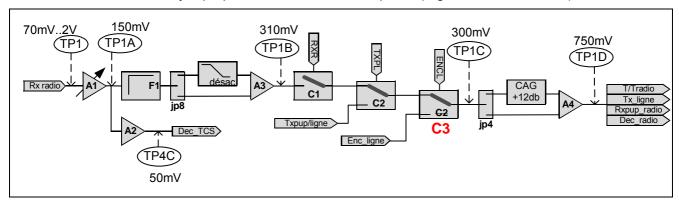

#### 3.1.2 FP2, INTERFACE PHONIE

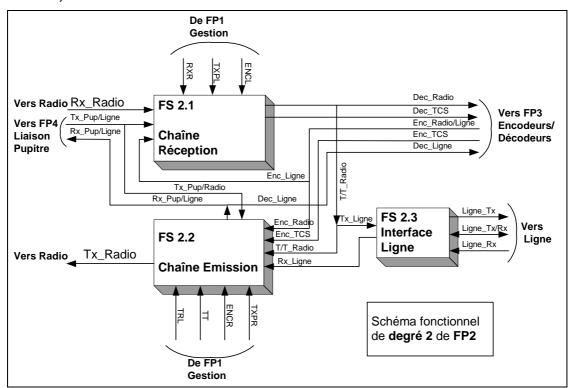

Figure 3.3 Schéma fonctionnel de degré 2 de FP2

Elle permet l'adaptation et l'aiguillage des signaux audiofréquence entre la radio, le pupitre optionnel (composé d'un microphone, d'un haut-parleur et d'un poussoir) et les circuits de codage/décodage (FP3).

#### 3.1.2.1 FS 2.1 Chaîne Réception

Elle reçoit le signal BF issu de la radio (Rx\_Radio); ce signal, après amplification est envoyé à FP3 pour le décodage TCS (Dec\_TCS).

Le signal Txpup/ligne (destiné au pupitre ou à la ligne), le signal Enc\_ligne (destiné à la ligne et issu des encodeurs) et le signal Rx\_Radio (après avoir subi une adaptation) sont aiguillés vers un contrôle automatique de gain avant d'être dirigés soit vers les décodeurs (Dec\_Radio), soit vers la ligne (Tx\_ligne), soit vers la chaîne émission (T/T\_Radio).

Les signaux RXR, TXPL et ENCL permettent d'aiguiller respectivement les signaux Rx\_Radio, Txpup/ligne et Enc\_ligne vers le CAG.

#### 3.1.2.2 FS 2.2 Chaîne Emission

Elle reçoit les signaux à émettre (Enc\_Radio, Enc\_TCS, T/T\_Radio et Rx\_ligne) soit vers la radio (Tx\_radio), soit vers le pupitre ou vers la ligne (Rx\_pup/ligne) soit vers les décodeurs (Dec\_ligne) en fonction des ordres d'aiguillage : TRL (transmission Radio), TT (Relayage direct), ENCR (Encodage Radio) et TXPR (émission pupitre).

### 3.1.2.3 FS 2.3 Interface ligne.

Elle permet l'adaptation, l'amplification et le filtrage des signaux de FS 2.1 vers la ligne de communication et inversement de la ligne de communication vers FS 2.2.

Elle peut fonctionner en simplex, les deux canaux Rx\_Ligne et Tx\_Ligne sont dirigés sur Ligne\_Tx/Rx; ou en duplex les canaux sont indépendants Ligne\_Rx est dirigé vers Rx\_Ligne et Tx\_Ligne est dirigé vers Ligne Tx.

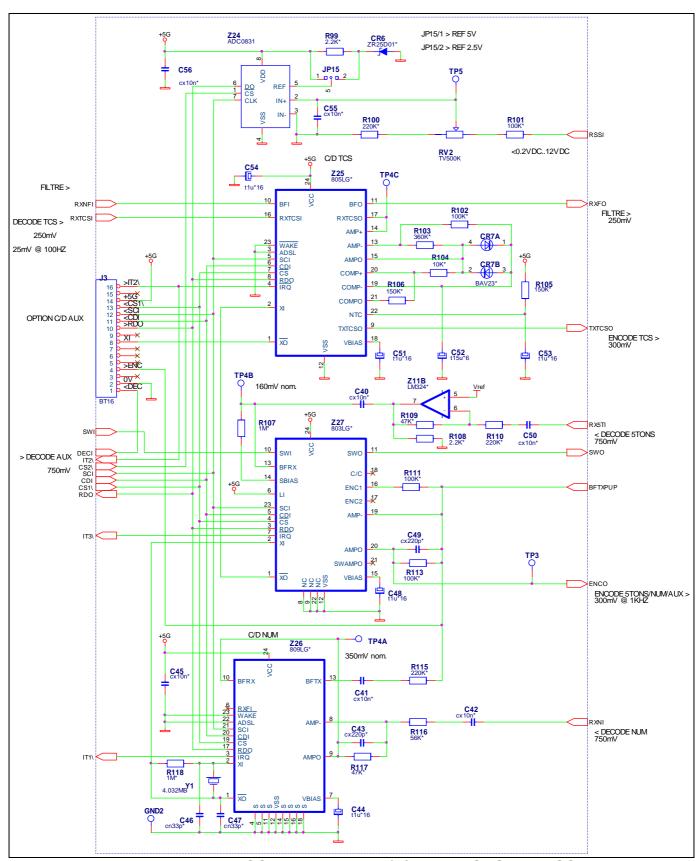

#### 3.1.3 FP3 CODAGE/DECODAGE

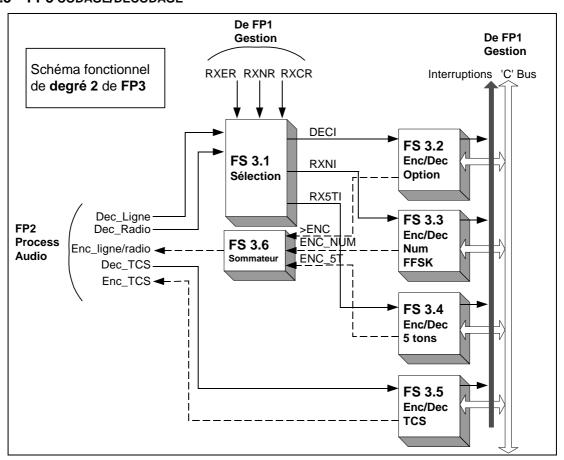

Figure 3.4: Schéma fonctionnel de degré 2 de FP3

Elle permet le codage/décodage des trames FFSK, TCS et 5 Tons, qui seront exploitées par FP1.

#### 3.1.3.1 FS 3.1 Sélection

Elle permet d'aiguiller les signaux Dec\_Ligne ou Dec\_Radio vers FS 3.2, FS 3.3 et FS 3.4; le co-deur TCS (FS 3.5) recoit directement son signal de FP 2.

### 3.1.3.2 FS 3.2 Enc/Dec option

Il s'agit d'une possibilité de rajouter un CODEC non prévu initialement, il doit être, comme les autres géré par le "C" Bus.

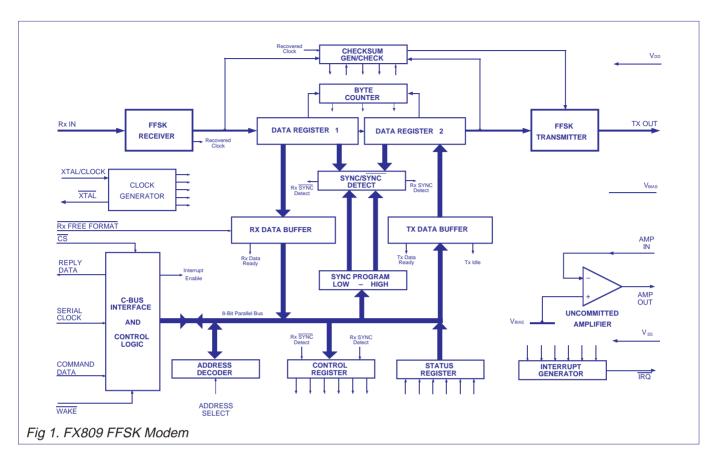

#### 3.1.3.3 FS 3.3 Enc/Dec numérique FFSK

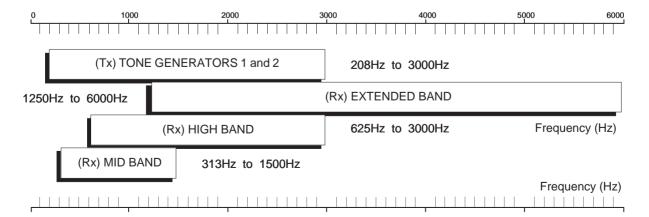

Réalisée autour du FX809, elle permet l'encodage et le décodage des données numériques modulées en FFSK (Fast Frequency Shift Keying) à 1 200 bauds, dans la bande passante des émetteurs / récepteurs radio. Le protocole supporté répond à la norme MPT13271 et décharge le microcontrôleur de ce travail (une trame = préambule + synchro + adresses + données + checksum). Par contre l'analyse du contenu des trames est confiée à FP1.

#### 3.1.3.4 FS 3.4 Enc/Dec "5 tons"

Réalisée autour du FX803, elle permet l'encodage et le décodage de trames dites "5 tons". Elle est également gérée par le microcontrôleur via le "C" bus.

Le circuit accepte les normes ZVEI, DZVEI, CCIR et EEA. Ce sont des normes de signalisation à basse fréquence, mais dans la bande passante audio (800 à 2 800 Hz suivant les normes), d'où le terme de "tons". Suivant les normes, 13 à 15 caractères peuvent être codés. Une trame se compose de 5 co-

<sup>&</sup>lt;sup>1</sup> MPT 1327 est un standard, à l'origine anglais, de communication analogique interurbaine permettant de relayer des ordres ou des états en format série asynchrone. Initialement le MPT1327 fonctionnait en VHF.

des successifs, d'où le nom de 5 "tons". Contrairement au DTMF (*Dual Tone Modulated Frequencies*), chaque code correspond à une seule fréquence. Le circuit accepte aussi le DTMF.

Ici, il n'est utilisé qu'en séquentiel 5 tons.

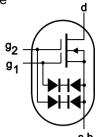

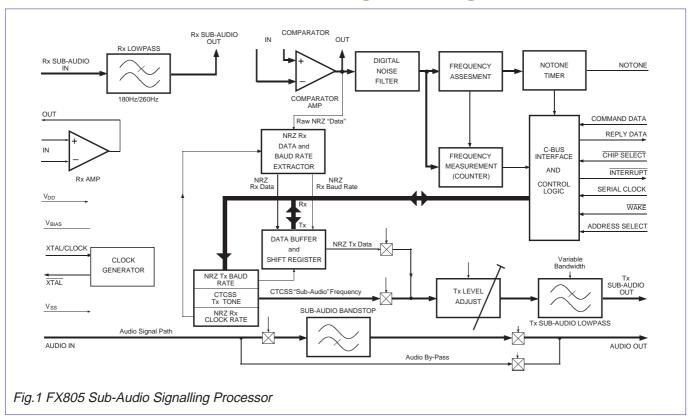

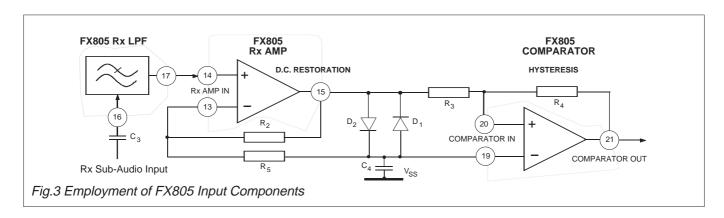

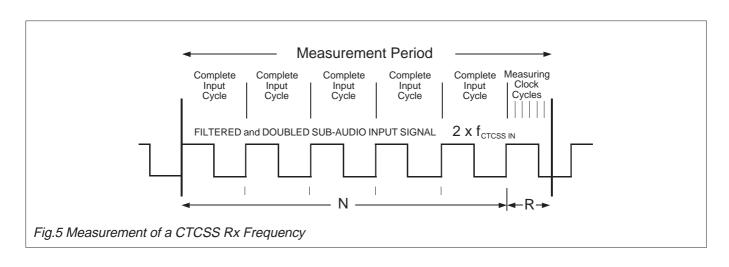

#### 3.1.3.5 FS 3.5 Enc/Dec "TCS"

Réalisée autour du FX805, elle permet l'encodage et le décodage de trames dites "TCS" (Tone Controlled Squelch). Elle est également gérée par le microcontrôleur via le "C" bus.

Le TCS est un codage fréquentiel en bande sub-audio (67 à 250,3 Hz la bande audio ne commençant qu'à 300 Hz). 38 codes sont ainsi réalisés. Voir figure 7-bis du dossier « schémas ».

#### 3.1.3.6 FS 3.6 Sommateur

Les signaux issus de FS 3.2, FS 3.3 et FS 3.4 sont sommés avant d'être dirigés vers FP2. Le signal issu du décodeur TCS est directement sorti.

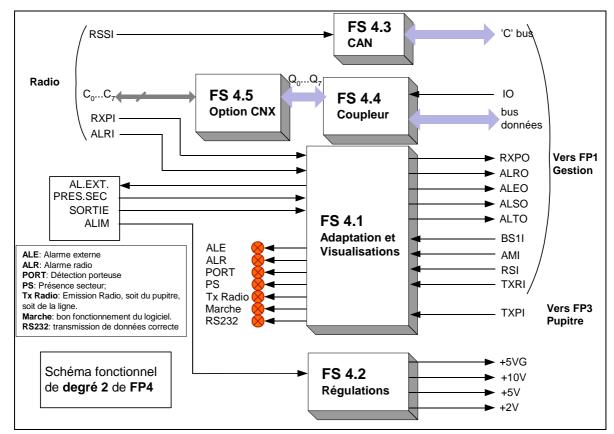

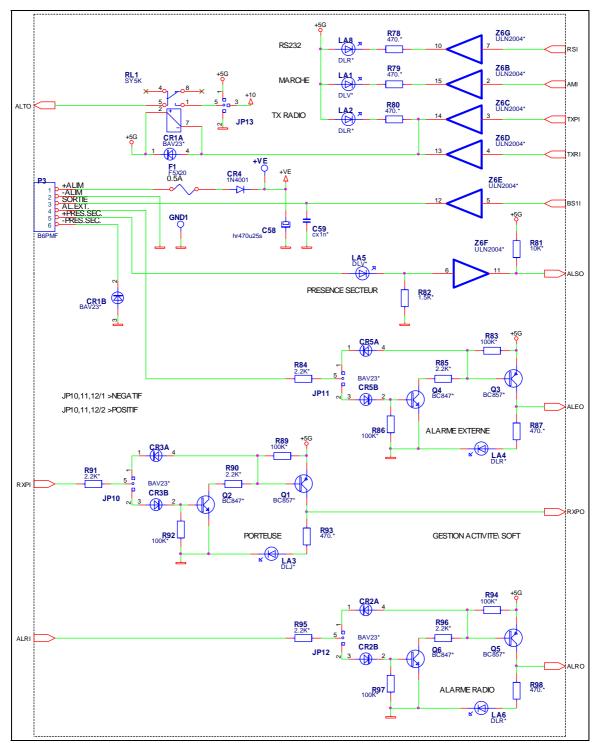

#### 3.1.4 FP4 ENTREES/SORTIES

Elle permet la visualisation des états du système, l'adaptation électrique de signaux d'alarmes et d'information en provenance de la radio, de l'alimentation secteur.

#### 3.1.4.1 FS 4.1 Adaptation et visualisation

Cette fonction adapte les niveaux issus de la radio, de l'alimentation vers FP1 et inversement les niveaux logiques de FP1 pour allumer des LEDs.

## 3.1.4.2 FS 4.2 Régulations

C'est un ensemble de régulateurs linéaires qui, à partir de l'alimentation principale (11 à 15 V DC) fournit:

- 2 alimentations de 5 V,

- 1 alimentation de 10 V,

- 1 tension de référence de 2 V pour les amplificateurs.

Figure 3.5: Schéma fonctionnel de degré de FP4

#### 3.1.4.3 FS 4.3 CAN

Il s'agit d'une fonction chargée de la conversion analogique numérique du signal RSSI issu du poste radio. Le signal RSSI donne une image logarithmique de la puissance reçue par le poste. Cette information permettra au voteur de décider qui est le relais le plus favorable.

Cette fonction fournit le résultat de conversion à FP1 via le "C" bus.

#### 3.1.4.4 FS 4.4 Coupleur (port de sortie)

C'est un simple port de sortie sur 8 bits destiné à piloter l'option connexion.

#### 3.1.4.5 FS 4.5 Option CNX

C'est une option sous forme de carte enfichable qui permet de piloter le changement de canaux des radios FM1000. Il en existe plusieurs versions.

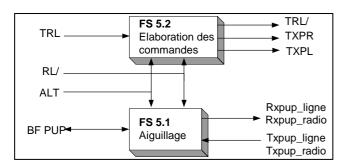

#### 3.1.5 FP 5 LIAISON PUPITRE

FS 5.1: Cette fonction, à partir de l'information ALT (poussoir d'alternat du pupitre) et RL/ issue de FP1, permet d'aiguiller la BF soit vers Txpup\_ligne et Txpup\_radio soit vers Rxpup\_ligne et Rxpup\_radio.

FS 5.2 : Les signaux TRL/, TXPR et TXPL sont élaborés par une simple logique combinatoire.

Figure 3.6 Schéma fonctionnel de degré 2 de FP5

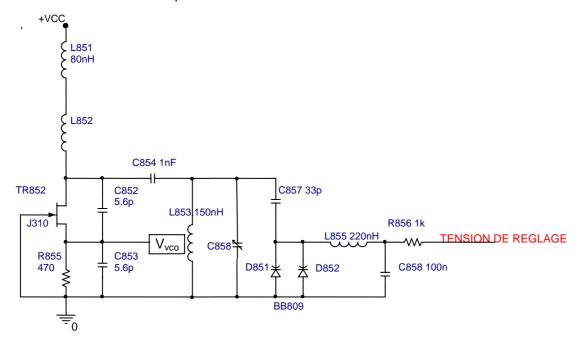

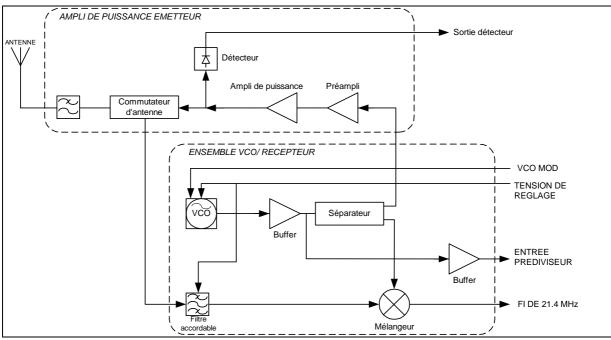

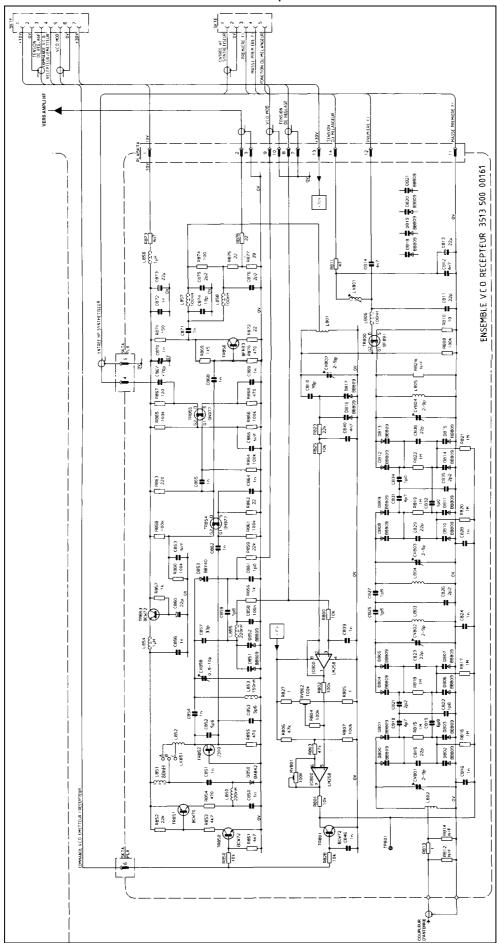

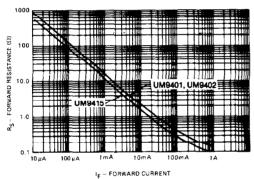

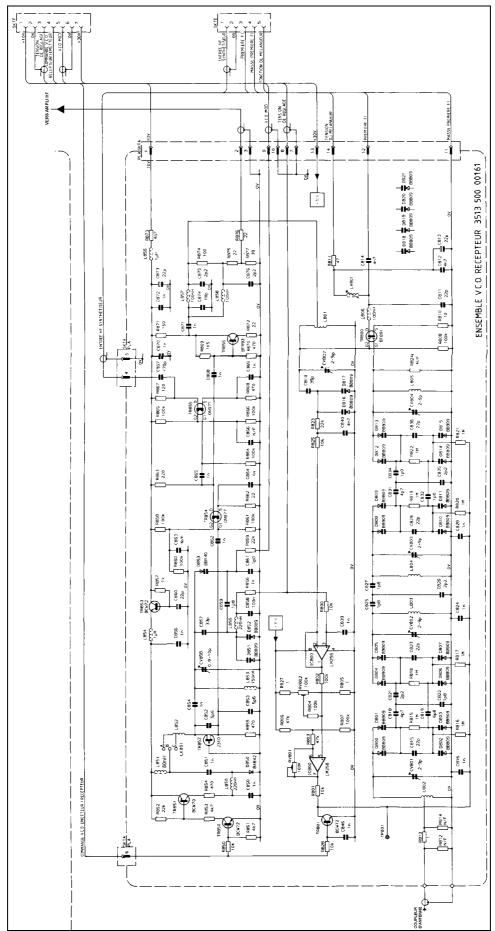

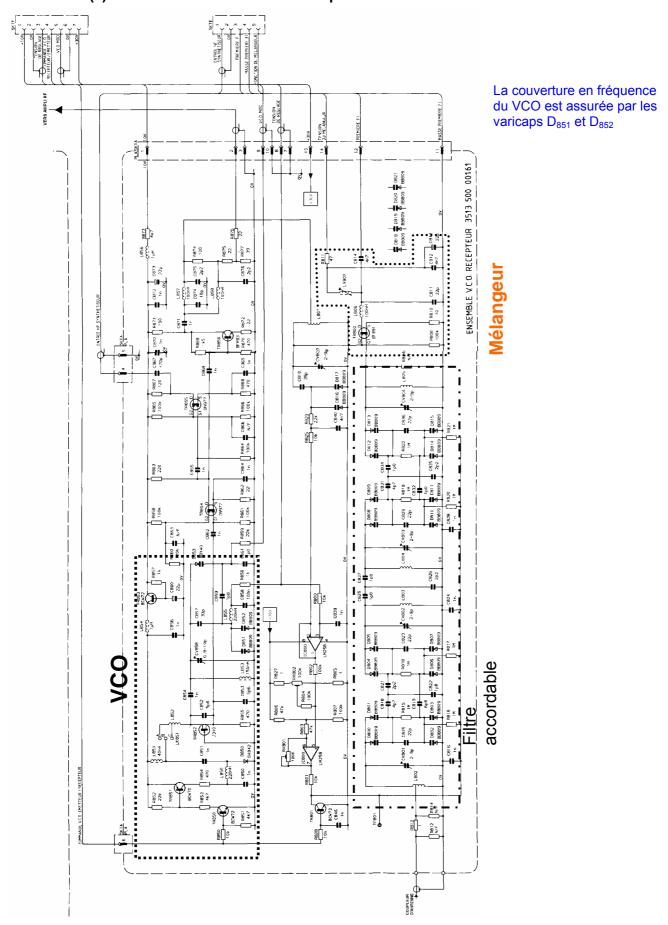

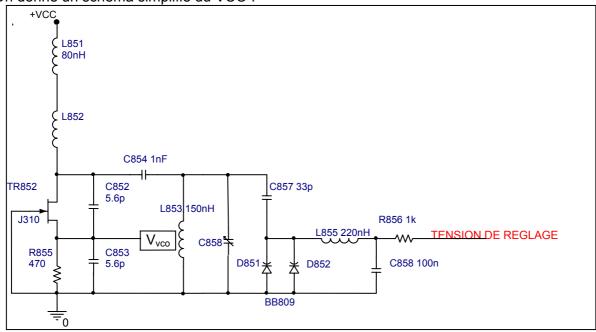

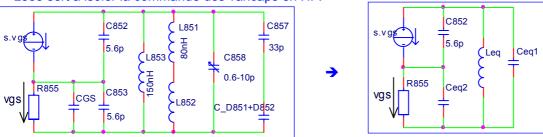

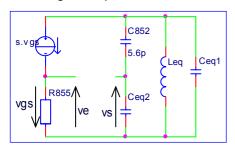

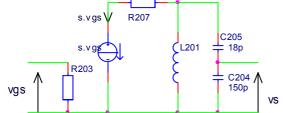

# 3.2 LES EMETTEURS RECEPTEURS FM1000

Ce sont des produits fabriqués et commercialisés par Philips, ils existent dans les bandes suivantes :

| Bande E0 | 68 - 88 MHz   |          |               |

|----------|---------------|----------|---------------|

| Bande B0 | 132 - 156 MHz | Bande A9 | 146 - 174 MHz |

|          |               |          |               |

| Bande K1 | 174 - 208 MHz | Bande K2 | 192 - 225 MHz |

|          |               |          |               |

| Bande TM | 400 - 440 MHz | Bande TA | 425 - 450 MHz |

| Bande U0 | 440 - 470 MHz | Bande WM | 470 - 520 MHz |

Espacement des canaux :

On trouvera page 9 du dossier « 'Schémas », deux extraits de schémas « synoptiques », présents dans la notice technique des postes FM1000.

Ce sont des postes en FM performants dont la puissance d'émission peut atteindre 30 W dans la bande E0 et 25 W dans les autres bandes. La puissance d'émission est programmable (1 W, 6 W, 10 W, 15 W, 25 W et 30 W).

Sur ces postes, SYSTEL n'utilise que la partie purement radio avec un espacement de 12,5 kHz et n'utilise pas les possibilités TCS et 5 tons des postes. Le signal RSSI est directement pris sur la carte récepteur après le démodulateur. La BF reçue est extraite avant les amplificateurs de volume. La BF à émettre est câblée après l'ampli microphone et les filtres du FM1000.

## 4 LES TRAMES

Description de quelques trames de commande et de contrôle.

#### 4.1 LES PARAMETRES

Ils sont logés en E2PROM, localement avec l'outil de paramétrage, via la liaison série.

### 4.1.1 LES PARAMETRES SIGNALISATION (T)

Les TCS: Sélection, Direct, Général, Réseau, Zone : de 00 à 38 sélectivité décodage TCS : SE = +/-0.5%, SL = +/-1%.

Les 5 tons : Appel, Identité, Commun , Mode , Boucle , AlarmeDébut , AlarmeFin , FinCom. 4 standards de codage ou décodage : C (ccir), E (eea), Z (zvei), D (dzvei), 5 ou 6 tons.

#### 4.1.2 LES PARAMETRES TEMPS (T)

Tx delai : TC (très court = 0,1 s), C (court = 0,15 s), N (normal = 0,2 s), L (long = 0,25 s).

Tonalité invitation: N (normal = 0.5 s), L (long = 1 s).

fin com : N (normal = 5 s), L (long = 10 s).

Tx max : C (court = 1 mn), N (normal = 2 mn), L (long = 3 mn), TL (très long = 4 mn)

#### 4.1.3 LES PARAMETRES RESEAU

Numéro relais réseau : de 01 à 16 Numéro relais zone : de 01 à 08 (t) Numéro département : de 01 à 99

Numéro réseau : de 00 à 24 Numéro zone : de 00 à 07 (t) Libellé du relais : 12 caractères

Mode auto: "B" ou "F" (t)

#### 4.1.4 PARAMETRES RADIO

Type de relais : Boxer, Racer, Autre, PRF

Type de récepteur: F (Philips fm1000), P (Philips prm), M(moto 900), A (autre), R (philipsPRF10)

Valeurs paliers RSSI: tensions (0,00 V à 5,00 V)

RSSI: VP (valeur + palier), P (palier)

#### 4.2 LES TRAMES NUMERIQUES RADIO

#### 4.2.1 STRUCTURE COMMUNE

#### 4.2.1.1 Préambule

2 premiers octets destinés à synchroniser la partie analogique du décodeur : AA AA

#### 4.2.1.2 Synchro ou clé

2 octets qui suivent le préambule, et signale le début d'une séguence valide : B4 33

#### 4.2.1.3 Données

Paquet de 6 octets d'informations comportant les fonctions et les données.

## 4.2.1.4 Contrôle ou CRC:

2 octets qui suivent le paquet de données.

C'est le résultat d'un polynôme (norme 1382) appliqué au paquet de données précédent, permettant la détection et la correction d'erreurs.

# 4.2.2 TRAME CONTROLE RESEAU PHONIE CTRL (CTX> RELAIS)

| Paquet 1 |                               |         |                   |              |          | Paquet 2 |          |         |       |       |       |        |       |       |

|----------|-------------------------------|---------|-------------------|--------------|----------|----------|----------|---------|-------|-------|-------|--------|-------|-------|

| Destina  | ation                         | Origine | Relais 1 Relais 2 |              | Relais 1 |          | s 2      | Rela    | ais 3 | Rel   | ais 4 | Rela   | ais 5 |       |

|          |                               |         |                   | d1           | d2       | d1       | 1        | d2      | d1    | d2    | d1    | d2     | d1    | d2    |

| Paquet 3 |                               |         |                   |              |          |          | Paquet 4 |         |       |       |       |        |       |       |

| Rel      | ais 6                         |         | Rela              | ais 7        |          | Re       | lais 8   | 8       | Rela  | ais 9 | Rela  | ais 10 | Rela  | is 11 |

| d1       | d2                            | d       | 1                 | d2           | ?        | d1       | (        | d2      | d1    | d2    | d1    | d2     | d1    | d2    |

|          |                               |         | Paqı              | ıet 5        |          |          |          |         |       |       | Paq   | juet 6 |       |       |

| Rela     | Relais 12 Relais 13 Relais 14 |         | 14                | Relais 15 Re |          | Rela     | ais 16   | non uti | lisé  |       |       |        |       |       |

| d1       | d2                            | d       | 1                 | d2           | ?        | d1       | (        | d2      | d1    | d2    | d1    | d2     | 00    | 00    |

#### 4.2.2.1 Destination

| bit 7 | bit 6               | bit 5 | bit 4 | bit 3     | bit 2    | bit 1     | bit 0 |

|-------|---------------------|-------|-------|-----------|----------|-----------|-------|

|       | TYPE                |       |       |           | Nombre   | )         |       |

| 001 = | 001 = relais phonie |       |       | nbre rela | ais rése | au : 01 . | 16    |

## 4.2.2.2 Origine

| bit 7   | bit 6 | bit 5                   | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |  |  |  |  |

|---------|-------|-------------------------|-------|-------|-------|-------|-------|--|--|--|--|

| TYPE    |       | IDENTITE                |       |       |       |       |       |  |  |  |  |

| CTX = 0 |       | n° du département: 0099 |       |       |       |       |       |  |  |  |  |

## 4.2.2.3 Relais

|               | d1                                    |                                     |       |       |       |                                 |               |  |  |  |  |

|---------------|---------------------------------------|-------------------------------------|-------|-------|-------|---------------------------------|---------------|--|--|--|--|

| bit 7         | bit 6                                 | bit 5                               | bit 4 | bit 3 | bit 2 | bit 1                           | bit 0         |  |  |  |  |

| N/S           | M                                     | S                                   | P3    | P2    | P1    | TX                              | RX            |  |  |  |  |

| 1<br>non géré | 0 = Mode auto<br>1 = Mode Ma-<br>nuel | 0 = non sélec-<br>té<br>1 = sélecté | 011   |       |       | 0 = Pw haute<br>1 = Pw<br>Basse | 0<br>non géré |  |  |  |  |

|                         |       |                  |          | d2       |                   |          |          |

|-------------------------|-------|------------------|----------|----------|-------------------|----------|----------|

| bit 7                   | bit 6 | bit 5            | bit 4    | bit 3    | bit 2             | bit 1    | bit 0    |

| C2                      | C1    | E                | 0        | 0        | IR                | 1 AL     |          |

| 0                       | 0     | 0 = éligible     | 0        | 0        | 0 = normal        | 1        | 0        |

| non géré 1 = non éligib |       | 1 = non éligible | non géré | non géré | 1 = interconnecté | non géré | non géré |

# 4.2.3 TRAME APPEL PHONIE (RELAIS > CTX)

| Destination | Origine | Fonction | Réseau | Param. 1 | Param. 2 |

|-------------|---------|----------|--------|----------|----------|

|-------------|---------|----------|--------|----------|----------|

#### 4.2.3.1 Destinataire

| bit 7        | bit 6                               | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |  |  |  |

|--------------|-------------------------------------|-------|-------|-------|-------|-------|-------|--|--|--|

| TYPE CTX = 0 | CTX = 0 IDENTITE département : 0099 |       |       |       |       |       |       |  |  |  |

## 4.2.3.2 Origine

| bit 7 | bit 6   | bit 5          | bit 4 | bit 3     | bit 2    | bit 1   | bit 0 |

|-------|---------|----------------|-------|-----------|----------|---------|-------|

| relai | s phoni | e = <i>001</i> |       | n° relais | s réseal | u :0116 | Ĉ     |

#### 4.2.3.3 Réseau

| bit 7     |  | l | bit 4         | bit 3 | bit 2 | bit 1 | bit 0 |  |

|-----------|--|---|---------------|-------|-------|-------|-------|--|

| ZONE : 07 |  |   | RESEAU : 0024 |       |       |       |       |  |

#### 4.2.3.4 Fonctions, paramètres

| Fonction | label | Désignation                             | Param. 1                              | Désignation                     | Param. 2 | Désignation           |  |  |

|----------|-------|-----------------------------------------|---------------------------------------|---------------------------------|----------|-----------------------|--|--|

| 00       | DRLX  | Début relayage                          | 00FF                                  | V.RSSI                          | 0108     | P.RSSI                |  |  |

| 01       | FRLX  | Fin relayage                            | 00                                    | Non utilisé                     | 00       | Non utilisé           |  |  |

| 02       | MRLE  | Marquage élection réseau                | 00FF                                  | V.RSSI                          | 0188     | P.RSSI                |  |  |

| 03       | FRLE  | Fin relayage élection                   | 00                                    | Non utilisé                     | 00       | Non utilisé           |  |  |

|          |       |                                         |                                       |                                 | 05       | Secteur               |  |  |

| 04       | DALR  | Début Alarme.                           | 00                                    | Non utilisé                     | 80       | Externe               |  |  |

|          |       |                                         |                                       |                                 | 09       | Radio                 |  |  |

|          |       |                                         |                                       |                                 | 05       | Secteur               |  |  |

| 05       | FALR  | Fin Alarme.                             | 00                                    | Non utilisé                     | 08       | Externe               |  |  |

|          |       |                                         |                                       |                                 | 09       | Radio                 |  |  |

| 08       | RTMP  | Réponse test mode/position              | (d1)CTRL                              | si mode auto:<br>TX = B(0)/F(1) | (d2)CTRL | si alarme : AL = 1    |  |  |

| 09       | ATPE  | Acquit téléparam écriture               | 0001                                  | 00 = valide                     | 00FF     | fonction écrite       |  |  |

| 0A       | ARLE  | Acquit Relais Elu                       | 00                                    | 01 = non valide                 | 00       | Non utiliaá           |  |  |

| OB       | MRLS  |                                         | 00FF                                  | Non utilisé<br>V.RSSI           | 0108     | Non utilisé<br>P.RSSI |  |  |

|          |       | Marquage sélection                      | 00FF                                  |                                 |          |                       |  |  |

| OC<br>OD | FRLS  | Fin relayage sélection  Début RX mobile | 00                                    | Non utilisé                     | 00       | Non utilisé           |  |  |

|          | DRXR  |                                         |                                       | Non utilisé                     | 00       | Non utilisé           |  |  |

| 0E<br>0F | FRXR  | Fin RX mobile                           | 00                                    | Non utilisé<br>V.RSSI           | 00       | Non utilisé           |  |  |

|          | MRZE  | Marquage élection zone                  | 00FF                                  |                                 | 0188     | Relais zone +P.RSSI   |  |  |

| 10       | RTTS  | Réponse test param temps                | voir lecture paramètres temps         |                                 |          |                       |  |  |

| 11       | RTSC  | Réponse test paramTCS                   | voir lecture paramètres TCS           |                                 |          |                       |  |  |

| 12       | RTSS  | Réponse test param 5 tons               | voir lecture paramètres 5 tons        |                                 |          |                       |  |  |

| 13       | RTRR  | Réponse test param radio                | voir lecture paramètres radio         |                                 |          |                       |  |  |

| EE       | RTEE  | Réponse test écriture E2P. 00FF adresse |                                       |                                 | 00FF     | donnée                |  |  |

| FF       | RTCF  | Réponse test configuration              | voir lecture paramètres configuration |                                 |          |                       |  |  |

#### 4.2.3.5 Param 2, fonction MRZE

| bit 7 | bit 6    | bit 5    | bit 4             | bit 3   | bit 2   | bit 1 | bit 0 |

|-------|----------|----------|-------------------|---------|---------|-------|-------|

| n°    | relais z | one : 0. | Pallier RSSI : 18 |         |         |       |       |

| (     | si appe  | I TCSZ)  | Ра                | iller K | 331 . I | 0     |       |

## 4.3 MODE 0, 1, 2, 3 ET 4

Non étudié

# 4.4 MODE AUTO OU MODE CONTROLE

Ce mode de fonctionnement est activé par le CTX en radio, à réception de la trame numérique contrôle "CTRL" comportant l'indication mode auto (ou électif) sans distinction "auto1" (puissance faible) ou "auto2" (blocage).

Ce mode permet l'élection ou la sélection d'un relais par un mobile, après contrôle de la base.

## 4.4.1 APPEL MOBILE

#### 4.4.1.1 Inscription et élection

Le relais est appelé par une des trois conditions :

- o Porteuse et TCSG présents 0,5 s minimum, 5 s maximum ;

- o Code 5/6 tons "C";

- o Porteuse et TCSG et code "C".

Si tel est le cas, la trame appel "MRLE" est émise avec un temps de décalage "tdrl" lié au numéro du relais. Ce temps est calculé comme suit ; (RL - 1) \* tdrl, avec tdrl min = 0.25 s, tdrl nom = 0.3 s et tdrl max = 0.35 s.

L'élection est effectuée à la réception de la trame "CTRL"comportant l'indication "relais élu"qui seule permet le relayage et l'identification.

Le test J1 indique un temps calculé comme suit : [(RLmax -RLn)\* tdrl] + (tdtp + txdn + tctrl + tte), où :

tdtp est le temps max de la télécommande numérique ligne (0,32 s max), txdn le tx delai du point bas(0,25 s max), tctrl le temps max de la trame contrôle (0,2 s), tte le temps de traitement de l'élection au point bas (0,01 s max), le temps de contrôle : tdp+txdn+tcrl+tte représente 780 ms max, tdrl = txdn + ttmrl + trdn, avec ttmrl = 83 ms et trdn = 5 ms, trdl max = 338 ms et tdrl min = 238 ms

## Phase d'inscription avant élection

Pour 16 relais, sur le relais 1, par exemple, le temps d'attente est de 4,35 s min et 5,85 s max. Idem sur le relais 16, le temps d'attente est de 780 ms.

#### 4.4.1.2 Sélection

Le relais est appelé par une des conditions :

- o Porteuse et TCSS sans condition de temps ;

- o code 5/6 tons "A" ;

- o porteuse et TCSS et code "A".

La trame numérique appel "MRLS" est émise après une de ces conditions.

Seule la réception de la trame "CTRL" comportant l'indication "relais sélecté" permet le relayage et l'identification.

# 5 DETECTION ET CORRECTION DES ERREURS DE TRANSMISSION

## 5.1 CODE DE REDONDANCE CYCLIQUE (CRC)

La transmission n'est pas toujours parfaite, les trames transmises peuvent contenir des erreurs. Pour garantir la fiabilité de la transmission on calcule le Code à Redondance Cyclique ou CRC puis on l'ajoute à la trame suivant le format MPT1327 compatible avec le circuit FX809 (CODEC FFSK). Le principe du calcul du CRC est le suivant :

Une trame de m bits est représentée par un polynôme de m termes notés :

$$x^{m-1} + x^{m-2} + \dots x^{0}$$

$\rightarrow$  Exemple 1001001  $\rightarrow$   $1*x^{6} + 0*x^{5} + \dots 1*x^{0}$

En arithmétique polynomiale, toutes les opérations sont effectuées modulo 2 sans reste : l'addition et la soustraction correspondent alors à l'opération OU EXCLUSIF.

Pour calculer la somme de contrôle, l'émetteur et le récepteur de données se mettent d'accord sur un polynôme générateur G(x) de degrés r de la forme xr + ... + x0.

La trame à transmettre de m bits correspond à un polynôme M(x).

La somme de contrôle (CRC) R(x) ajoutée à la fin de la trame, est calculée de façon à ce que le polynôme M(x)R(x) soit divisible par G(x).

La sécurité de la transmission peut encore être renforcée en ajoutant à la trame un bit de parité. Par exemple si G(x) est de degrés 15, le CRC est de 15 bits. Il reste alors un bit disponible dans le dernier octet de la trame. Ce bit est disponible pour rendre toute la trame paire.

#### 5.2 ALGORITHME DE CALCUL DU CODE DE REDONDANCE CYCLIQUE

Les messages à transmettre ont une longueur constante égale à 6 octets. Dans le cas de messages plus longs, par exemple pour la trame de contrôle réseau phonie (CTRL) le message est découpé en paquets de 6 octets.

Soit M(x) le polynôme correspondant au message à transmettre et G(x) le polynôme générateur de degrés r = 15 choisi :

$$G(x) = X15 + X14 + X13 + X11 + X4 + X2 + X0 (11101000 00010101)$$

Multiplier M(x) par xr, ce qui revient à ajouter r zéros à la fin du message.

Effectuer la division polynomiale

$$\frac{M(x)x^r}{G(x)} = Q(x) + R(x)$$

Le quotient Q(x) est ignoré, le reste R(x) (CRC) contient r bits.

#### 5.3 MISE AU FORMAT MPT1327

Le coefficient  $X^0$  du reste R(x) est inversé, puis R(x) est multiplié par deux pour former un mots de 16 bits : R'(x).

La trame à transmettre est T'(x) = M(x) - R'(x) + p, p étant un bit de parité de la trame T(x) calculé avec les bits 1 à 63. Ce bit est ajouté afin de rendre la parité de la trame toujours paire.

La Figure 5.1 page 24 présente un exemple de calcul d'une trame T'x().

#### 5.4 RECEPTION DE LA TRAME ET VERIFICATION

Pour vérifier qu'une trame a été correctement transmise, on effectue les opérations suivantes :

La parité de la trame est vérifiée (elle doit être paire), puis le bit 63 est inversé.

Les 63 premiers bits sont utilisés comme coefficients X77 à X15 d'un polynôme de 77 bits qui sera utilisé comme dividende par le générateur G(x).

Si 15 bits du reste de la division sont nuls, la trame a été correctement transmise.

Les 15 bits (x15..x1) du reste de la division sont utilisés pour former un mot de 16 bits appelé syndrome. Le bit 0 est positionné à la valeur 1 si la parité de la trame reçue est impaire. Ce syndrome peut fournir une indication sur les bits erronés.

Les Figure 5.2 page 25 et page 26 présentent chacune un exemple de calcul du syndrome.

#### 5.5 CORRECTION DES ERREURS

Les erreurs simples et doubles (adjacentes) dans la trame reçue peuvent être corrigées en comparant le syndrome avec les entrées de la table Figure 5.4 page 27.

Les syndromes 0003 ... 7FBB<sub>(16)</sub> correspondent à des erreurs doubles (parité inchangée), les valeurs 8000<sub>(16)</sub> ... FC69<sub>(16)</sub> correspondent à des erreurs simples (parité incorrecte).

Si une correspondance est trouvée, le(s) bit(s) à inverser est (sont) spécifié(s) par la colonne adjacente.

#### Exemple:

Trame T'(x) envoyée 6 octets :

erreur double

Trame T'(x) reçue :

Pour ce polynôme, le syndrome est 60<sub>(16)</sub> (voir page 26). Dans la table Figure 5.4 page 27, la correspondance avec ce syndrome donne pour numéro de bits erronés les valeurs 9 et 10.

Trame M(x)

Division  $\frac{M(x)x^r}{G(x)}$

```

11101000 00010101

1100001 10111110 1

1110100 00001010 1

10101 10110100 010

11101 00000010 101

1000 10110110 1110

1110 10000001 0101

110 00110111 10111

111 01000000 10101

1 01110111 0001010

1 11010000 0010101

10100111 00111111

11101000 00010101

1001111 00101010 1

1110100 00001010 1

111011 00100000 01

111010 00000101 01

1 00100101 0010111

1 11010000 0010101

11110101 00000101

11101000 00010101

11101 00010000 000

11101 00000010 101

10010 10110010 001

11101 00000010 101

1111 10110000 1001

1110 10000001 0101

1 00110001 1100010

1 11010000 0010101

11100001 11101110

11101000 00010101

1001 11111011 0000

1110 10000001 0101

111 01111010 01010

111 01000000 10101

111010 11111000 00

111010 00000101 01

11111101 0100000

Reste de la division avec dernier bit inversé

11111101 0100001

Trame T'(x) complète incluant le bit de parité (bit 64) ici à 0.

1.....

89

AB CD EF 12 34

```

Figure 5.1 : Construction d'une trame T'(x)

Etape 2 : inverser le bit 63, puis diviser les 63 premiers bits (décalés à gauche de 15 positions) par le polynôme G(x).

```

11101000 00010101

1100001 10111110 1

1110100 00001010 1

10101 10110100 010

11101 00000010 101

1000 10110110 1110

1110 10000001 0101

110 00110111 10111

111 01000000 10101

1 01110111 0001010

1 11010000 0010101

10100111 00111111

11101000 00010101

1001111 00101010 1

1110100 00001010 1

111011 00100000 01

111010 00000101 01

1 00100101 0010111

1 11010000 0010101

11110101 00000101

11101000 00010101

11101 00010000 000

11101 00000010 101

10010 10110010 001

11101 00000010 101

1111 10110000 1001

1110 10000001 0101

1 00110001 1100010

1 11010000 0010101

11100001 11101110

11101000 00010101

1001 11111011 1111

1110 10000001 0101

111 01111010 10101

111 01000000 10101

111010 00000101 01

111010 00000101 01

Reste de la division = 0000000 00000000

00000000 00000000

Syndrome :

Pas d'erreur détectée.

```

Figure 5.2 : Calcul du syndrome de la trame reçue sans erreur

Etape 1 : tester la parité : correcte

Etape 2 : inverser le bit 63, puis diviser les 63 premiers bits (décalés à gauche de 15 positions) par le polynôme G(x).

```

11101000 00010101

1100001 01111110 1

1110100 00001010 1

10101 01110100 010

11101 00000010 101

1000 01110110 1110

1110 10000001 0101

110 11110111 10111

111 01000000 10101

1 10110111 0001010

1 11010000 0010101

1100111 00111111 1

1110100 00001010 1

10011 00110101 011

11101 00000010 101

1110 00110111 1100

1110 10000001 0101

10110110 10011111

11101000 00010101

1011110 10001010 0

1110100 00001010 1

101010 10000000 10

111010 00000101 01

10000 10000101 110

11101 00000010 101

1101 10000111 0111

1110 10000001 0101

11 00000110 001000

11 10100000 010101

10100110 01110110

11101000 00010101

1001110 01100011 0

1110100 00001010 1

111010 01101001 10

111010 00000101 01

1101100 11110100 1

1110100 00001010 1

11000 11111110 011

11101 00000010 101

101 11111100 11011

111 01000000 10101

10 10111100 011101

11 10100000 010101

1 00011100 0010000

1 11010000 0010101

11001100 00001011

11101000 00010101

100100 00011110 01

111010 00000101 01

11110 00011011 000

11101 00000010 101

11 00011001 101000

11 10100000 010101

10111001 11110100

11101000 00010101

1010001 11100001 0

1110100 00001010 1

100101 11101011 10

111010 00000101 01

11111 11101110 110

11101 00000010 101

10 11101100 011000

11 10100000 010101

1 01001100 0011010

1 11010000 0010101

10011100 00011110

11101000 00010101

1110100 00001011 0

1110100 00001010 1

Reste de la division = 000000 01100000

0000000 00000001 100000

0000000 \ 01100000 \ (\ 0060_{(16)})

Syndrome :

```

Figure 5.3 : Calcul du syndrome de la trame comportant des erreurs

| Syndron | Syndrome Bits à Syndrome Bits à |    | Syndron | ne Bits à | Syndron | ne Bits à |         |         |         |

|---------|---------------------------------|----|---------|-----------|---------|-----------|---------|---------|---------|

| (hex) c | orrige                          | er | (hex)   | corrige   | r       | (hex) c   | orriger | (hex) c | orriger |

|         |                                 |    |         |           |         |           |         |         |         |

| 0003    | 14                              | 15 | 468D    | 40        | 41      | 8001      | 15      | B456    | 25      |

| 0006    | 13                              | 14 | 4841    | 61        | 62      | 8002      | 14      | B484    | 19      |

| 000C    | 12                              | 13 | 4989    | 33        | 34      | 8004      | 13      | B83F    | 62      |

| 0018    | 11                              | 12 | 4B7B    | 45        | 46      | 8008      | 12      | B887    | 34      |

| 0030    | 10                              | 11 | 4BD7    | 22        | 23      | 8010      | 11      | B929    | 46      |

| 0060    | 9                               | 10 | 4E0F    | 16        | 17      | 8020      | 10      | B94D    | 23      |

| 00C0    | 8                               | 9  | 502A    | 62        | 63      | 8040      | 9       | BA05    | 7       |

| 0180    | 7                               | 8  | 50CE    | 34        | 35      | 8080      | 8       | C000    | 1       |

| 0300    | 6                               | 7  | 51B7    | 46        | 47      | 8100      | 7       | C02E    | 36      |

| 0600    | 5                               | 6  | 51E1    | 23        | 24      | 8200      | 6       | C31C    | 50      |

| 0C00    | 4                               | 5  | 530D    | 17        | 18      | 8400      | 5       | C60A    | 39      |

| 15D3    | 43                              | 44 | 574C    | 41        | 42      | 8800      | 4       | C748    | 57      |

| 1763    | 20                              | 21 | 5A62    | 48        | 49      | 88E9      | 60      | C885    | 28      |

| 1800    | 3                               | 4  | 5CD1    | 47        | 48      | 8A09      | 32      | CA3E    | 54      |

| 18CD    | 28                              | 29 | 5CFA    | 24        | 25      | 8CB1      | 44      | D048    | 29      |

| 193B    | 59                              | 60 | 5D8C    | 18        | 19      | 8D21      | 21      | E401    | 38      |

| 1E1B    | 31                              | 32 | 6000    | 1         | 2       | 9000      | 3       | E588    | 41      |

| 21CD    | 56                              | 57 | 6039    | 36        | 37      | 90C7      | 52      | E685    | 56      |

| 220B    | 38                              | 39 | 6292    | 50        | 51      | 91D2      | 59      | E815    | 63      |

| 2867    | 35                              | 36 | 6334    | 26        | 27      | 9412      | 31      | E849    | 35      |

| 2BA6    | 42                              | 43 | 64EC    | 57        | 58      | 9962      | 43      | E89E    | 47      |

| 2D31    | 49                              | 50 | 650F    | 39        | 40      | 9A2B      | 26      | E8AC    | 24      |

| 2E7D    | 25                              | 26 | 6815    | 63        | 64      | 9A42      | 20      | E908    | 18      |

| 2EC6    | 19                              | 20 | 6CAE    | 52        | 53      | A000      | 2       | EE2D    | 49      |

| 3000    | 2                               | 3  | 6F21    | 54        | 55      | A017      | 37      | F07E    | 61      |

| 3149    | 51                              | 52 | 740B    | 15        | 16      | A18E      | 51      | F10E    | 33      |

| 319A    | 27                              | 28 | 786C    | 29        | 30      | A305      | 40      | F252    | 45      |

| 3276    | 58                              | 59 | 7897    | 60        | 61      | A3A4      | 58      | F29A    | 22      |

| 3657    | 53                              | 54 | 7B07    | 32        | 33      | A51F      | 55      | F40A    | 16      |

| 3C36    | 30                              | 31 | 7EE3    | 44        | 45      | A824      | 30      | F91F    | 27      |

| 439A    | 55                              | 56 | 7FBB    | 21        | 22      | B2C4      | 42      | FC69    | 53      |

| 4416    | 37                              | 38 | 8000    | 64        |         | B44F      | 48      | _       |         |

Figure 5.4 : Table de correction des bits erronés en fonction du syndrome

# 1 PREMIERE PARTIE: PROTOCOLES DE COMMUNICATION DU RESEAU D'ALERTE DES POMPIERS

#### 1.1 ETUDE PRELIMINAIRE

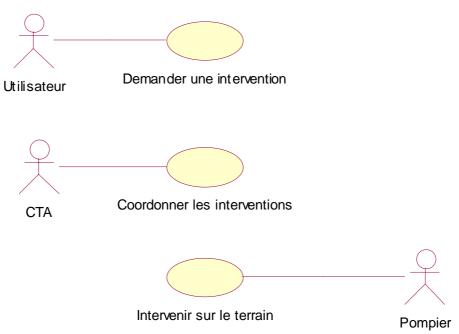

Q 1.1) Etablir le DIAGRAMME DE CAS D'UTILISATION préliminaire du réseau d'alerte des pompiers.

#### 1.2 ETABLISSEMENT D'UNE CONNEXION ENTRE UN POSTE MOBILE ET UN RELAIS

Le réseau d'alerte des pompiers est celui de la Charente Maritime (17). La zone couverte possède le numéro 1, le réseau étudié correspond au canal opérationnel (code 5). Cette zone comporte 6 relais éligibles non interconnectés. On s'intéressera ici uniquement au mécanisme permettant de mettre en relation un poste mobile avec le **C**entre de **T**raitement d'**A**lerte via le relais le mieux situé. La procédure d'élection est décrite dans le paragraphe *Election d'un relais* du document technique.

Dans cette configuration, les relais sont programmés en mode auto (voir paragraphe *mode auto ou mode contrôlé* du document technique) et en puissance d'émission haute.

Pour établir une communication, un poste mobile émet une porteuse et un code *TCSG*. La carte VTXCOM mesure le niveau de réception du signal dans le récepteur à l'aide d'un CAN et mémorise cette valeur sous la forme de deux codes : *V.RSSI* (niveau du signal) et *P.RSSI* (palier du signal).

On supposera ici que les relais 3 et 5 reçoivent la porteuse et un code *TCSG* valide. Les niveaux de réception *V.RSSI* sont respectivement 20 et 70, les paliers *P.RSSI* sont respectivement 5 pour le relais 3, et 5 pour le relais 5.

#### 1.2.1 PROTOCOLE D'ECHANGE DES TRAMES

**Q 1.2)** Etablir le diagramme de séquences permettant d'établir une communication entre un poste mobile et le Centre de Traitement d'Alerte (CTA). Ce diagramme devra mettre en évidence les messages échangés entres les candidats participant à l'établissement de la communication.

#### 1.2.2 COMPOSITION DES TRAMES ECHANGEES

- **Q 1.3) Préciser** le relais le plus approprié pour établir la communication entre le poste mobile et le Centre de Traitement d'Alerte (CTA).

- **Q 1.4) Donner** la composition de chaque trame échangée entre le relais 5 et le relais voteur (hors bits de synchronisation et de contrôle) (utiliser le dossier réponse).

#### 1.3 CONSTRUCTION ET DECODAGE DES TRAMES

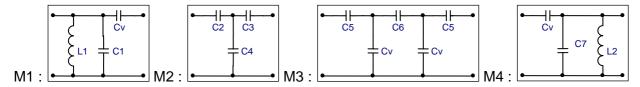

Les trames émises par les émetteurs des relais sont composées en mémoire dans la carte VTXCOM, puis sont transmises en série via le "C" BUS au circuit concerné. Celui-ci code la trame en fréquences audibles au format FFSK1382. Le circuit est programmé de façon à ne générer ni CRC, ni bit de parité. Ces éléments sont calculés par logiciel.

Les signaux reçus par le récepteur de chaque relais sont transmis au même circuit. Celui-ci décode les signaux et les communique au processeur via le bus série "C" BUS. Le processeur place ces trames brutes en mémoire afin d'être traitées. Le circuit est programmé de façon à ne pas générer de syndrome de trame, celui-ci est calculé par logiciel.

En cas d'erreur, le logiciel essaie de corriger les bits erronés.

#### 1.4 CONSTRUCTION DES TRAMES AU FORMAT MPT1327

On s'intéressera à la génération d'une trame T'(x) émise par un relais c'est-à-dire :

- o au calcul du CRC,

- o à la mise au format MPT1327.

- Q 1.5) Donner le composant utilisé pour générer et décoder les signaux FFSK1382.

- **Q 1.6)** On utilise le polynôme générateur  $G(x) = X^{15} + X^{14} + X^{13} + X^{11} + X^4 + X^2 + X^0$  de degré  $x^r$ .

**Calculer** le CRC  $R(x) = \frac{M(x).x^r}{G(x)}$  pour la trame M(x) ci-dessous.

|      |    |    |     | ı  |    |     |

|------|----|----|-----|----|----|-----|

|      |    |    |     |    |    | 1   |

| hex  | 11 | 23 | 0.2 | 25 | 14 | 0.5 |

| 1102 |    | 23 | 02  |    |    | 03  |

- **Q 1.7) Donner** la composition (en binaire) de la trame $T(x) = M(x).x^r R(x)$ . On placera à gauche les bits de poids fort.

- **Q 1.8)** Calculer  $R(x) = \frac{T(x)}{G(x)}$  pour cette trame.

- **Q 1.9) Démontrer** que le quotient et le reste de la division euclidienne des polynômes modulo 2 est unique.

- **Q 1.10) Donner** la composition (en hexadécimal) de la trame T'(x), format MPT1327, transmise.

- 1.5 VERIFICATION ET CORRECTION D'UNE TRAME RECUE

On suppose que la trame reçue comporte deux bits d'erronés : bits 7 et 8.

- **Q 1.11)** Calculer le syndrome pour une trame reçue comportant les bits 7 et 8 erronés. On fournira le résultat en base 16.

- Q 1.12) Raisonner et argumenter sur la capacité de ce syndrome à corriger ces erreurs.

## 2 DEUXIEME PARTIE: PROGRAMMATION DES TRAMES AU FORMAT MPT1327

On s'intéressera ici à :

- o la mise au format MPT1327 d'une trame brute,

- o au calcul du syndrome d'une trame recue,

- o à la correction des bits erronés dans une trame.

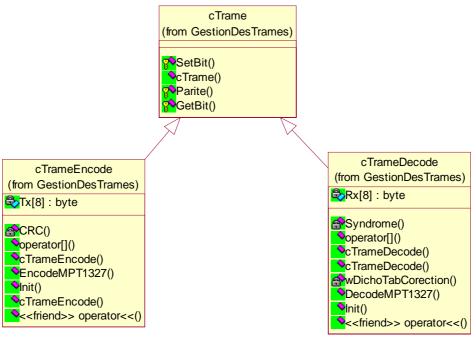

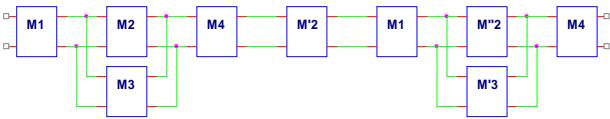

- 2.1 CLASSES D'ENCAPSULATION DE LA GESTION DES TRAMES

La gestion des trames est encapsulée dans trois classes comme le montre le diagramme statique de classes ci-dessous (Figure 2.1) :

La classe *cTrame* encapsule les fonctions communes aux classes *cTrameEncode* et *cTrameDecode*. Elle comporte des fonctions membres permettant :

- o d'obtenir un bit d'une trame,

- o de modifier un bit d'une trame,

- o de déterminer la parité d'une trame.

Cette classe ne comporte aucun attribut et un constructeur par défaut n'effectuant aucun action. Les types byte, ushort, word correspondent respectivement aux types unsigned char, unsigned short.

Figure 2.1

La classe *cTrameEncode* encode une trame brute au format MPT1327. Elle comporte une classe de gestion des exceptions *ErreurIndice* permettant de récupérer les erreurs provoquées par des indices hors trame. Cette classe possède un constructeur par défaut initialisant le vecteur *Tx* à 0 et un constructeur initialisant *Tx* à partir d'une trame non encodée.

La classe *cTrameDecode* décode une trame brute au format *MPT1327*. Elle comporte deux classes de gestion des exceptions *ErreurIndice* et *ErreurTrame*. Cette classe possède un constructeur par défaut initialisant le vecteur *Rx* à 0 et un constructeur initialisant *Rx* à partir d'une trame encodée.

- **Q 2.1) Déclarer** la classes cTrame (utiliser le dossier réponse). On s'aidera de la description des paramètres de fonction donnés dans le document réponse.

- **Q 2.2) Déclarer** la classe cTrameEncode (utiliser le dossier réponse). On s'aidera de la description des paramètres de fonction donnés dans le document réponse.

- **Q 2.3)** Déclarer la classe cTrameDecode (utiliser le dossier réponse). On s'aidera de la description des paramètres de fonction donnés dans le document réponse.

- **2.2** CODAGE DES FONCTIONS MEMBRES DE LA CLASSE *CTRAME*

- **Q 2.4) Donner** le code des fonctions membres GetBit et SetBit (utiliser le dossier réponse).

- Q 2.5) Donner le code de la fonction membre Parite (utiliser le dossier réponse).

- 2.3 CODAGE DES FONCTIONS MEMBRES DE LA CLASSE CTRAMEENCODE

- **Q 2.6)** Le constructeur cTrameEncode(const byte bTrame[]) reçoit en paramètre une trame brute qu'il recopie dans Tx aux indices 0..5. **Donner** le code de ce constructeur.

- NB : la fonction membre *Init* réalise le même code (utiliser le dossier réponse).

- **Q 2.7)** Cette classe possède également un constructeur par défaut. Dans le cas de l'application Réseau d'Alerte des Pompiers, **exprimer** l'intérêt qu'il y a à déclarer ce type de constructeur. **Justifier** dans ce cas la fonction membre Init (utiliser le dossier réponse).

- Q 2.8) Une fois les trames encodées, l'accès aux trames en lecture seule, s'effectue à l'aide de l'opérateur surchargé []. En cas de débordement d'indice une exception ErreurIndice est levée. **Donner** le code de cet opérateur (utiliser le dossier réponse).

- **Q 2.9)** La fonction membre CRC calcule le CRC de la trame (voir document technique). **Donner** le code de cette fonction (utiliser le dossier réponse).

- **Q 2.10)** La fonction membre EncodeMPT1327 encode la trame Tx au format MPT1327. **Donner** le code de cette fonction (utiliser le dossier réponse).

- **Q 2.11)** Afin de faciliter la mise au point, l'opérateur d'injection de flux << est surchargé pour cette classe. Il permet d'injecter le contenu d'une trame transcodée au format hexadécimal dans le flux passé en paramètre. **Donner** le code de cet opérateur (utiliser le dossier réponse).

#### **2.4** CODAGE DES FONCTIONS MEMBRES DE LA CLASSE *CTRAMEDECODE*

- Q 2.12) Le constructeur cTrameDecode(const byte bTrame[]) reçoit en paramètre une trame encodée au format MPT1327 qu'il copie dans Rx (indice 0..7). Nota : la fonction membre Init exécute le même code. Le syndrome de la trame est calculé par la fonction membre Syndrome suivant l'algorithme donné dans le dossier technique. **Donner** le code de la fonction membre Syndrome (utiliser le dossier réponse).

- Q 2.13) Un syndrome différent de zéro signifie qu'il y a eu erreur de transmission. La valeur du syndrome permet de déterminer les bits en erreur grâce à la table donnée dans le dossier technique figure 5.4. Déclarer une structure STRUCT\_ERROR\_CORRECTION décrivant un élément du tableau de correction (zone grisée figure 5.4 du dossier technique). Initialiser de façon statique un tableau tab\_error\_correction avec les éléments du tableau figure 5.4 (on donnera uniquement les deux premières lignes et la dernière ligne) (utiliser le dossier réponse).

- **Q 2.14)** La fonction membre wDichoTabCorection effectue une recherche dichotomique dans la table tab\_error\_correction en utilisant un syndrome comme clé. **Donner** le code de cette fonction (utiliser le dossier réponse).

- **Q 2.15)** La fonction membre DecodeMT1327 vérifie la validité de la trame reçue et en corrige les éventuelles erreurs. Si une erreur n'a pas pu être corrigée la fonction lève une exception ErreurTrame. **Donner** le code de cette fonction (utiliser le dossier réponse).

#### 2.5 TEST UNITAIRE

**Q 2.16)** Proposer un premier test unitaire encodant puis décodant la trame :

puis **proposer** un deuxième test permettant de vérifier la capacité de correction d'erreur du protocole MPT1327.

Les exceptions seront interceptées et gérées de façon suivante : une erreur de trame irrécupérable provoque un nouveau décodage avec une erreur corrigible. (utiliser le dossier réponse).

# 3 TROISIEME PARTIE « CONCEPTION D'UNE SEQUENCE PEDAGOGIQUE »

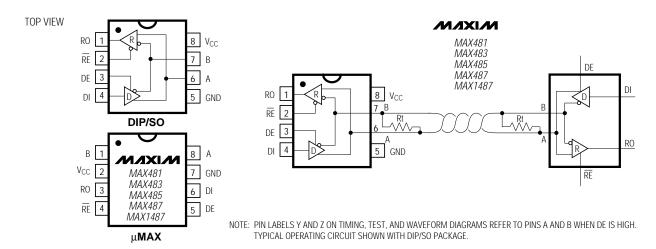

Les relais de retransmission et le relais *voteur* peuvent être connectés en réseau à l'aide de lignes spécialisées ou à l'aide de faisceaux hertziens. Dans ce type de configuration le connecteur J4 est relié à l'interface de communication et la connexion doit être établie en mode simplex. Le mode de transmission utilisé par les lignes spécialisées ou les faisceaux hertziens est transparent.

La procédure de vote s'effectue alors via le réseau, les trames envoyées sont identiques à celles de la transmission par radio.

## 3.1 QUESTIONS PRELIMINAIRES AU TRAVAIL PEDAGOGIQUE

- Q 3.1) Donner les domaines d'emploi des liaisons de type RS232, RS422, RS485.

- **Q 3.2)** Préciser quel type de connexion il faut établir afin de mettre en réseau les cartes VTXCOM. **Donner** les configurations et/ou modifications à apporter alors aux cartes VTXCOM.

- **Q 3.3) Nommer** les couches du modèle OSI sollicitées lors de l'élection d'un relais. **Préciser** les éléments sollicitant ces couches.

#### 3.2 ELABORATION D'UNE SEQUENCE PEDAGOGIQUE

**Q 3.4)** A partir du support « Réseau d'Alerte des Pompiers », et en vous inspirant de la mise en réseau des cartes VTXCOM, **élaborer** l'organisation d'une séquence d'enseignement destinée à des étudiants de BTS électronique ou d'informatique industrielle.

Vous devrez préciser :

- Le type de public à qui s'adresse cette séquence (type de BTS, année de formation, effectif, ...).

- L'objectif terminal visé de la séquence. Celle-ci doit être déterminée d'après les textes officiels qui régissent le BTS ainsi que les recommandations de l'inspection générale de la discipline.

- Les objectifs intermédiaires des différentes phases, les travaux proposés aux étudiants, les modes d'évaluation, la trame des évaluations, la durée des différentes phases.

- Les travaux produits par les élèves et la trame des réponses attendues par le professeur.

# 4 QUATRIEME PARTIE GESTION (FP 1)

- **4.1** DECODAGE D'ADRESSE (FS 1.3)

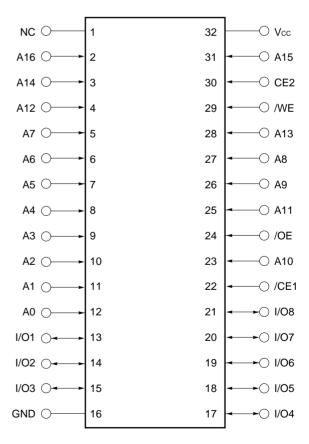

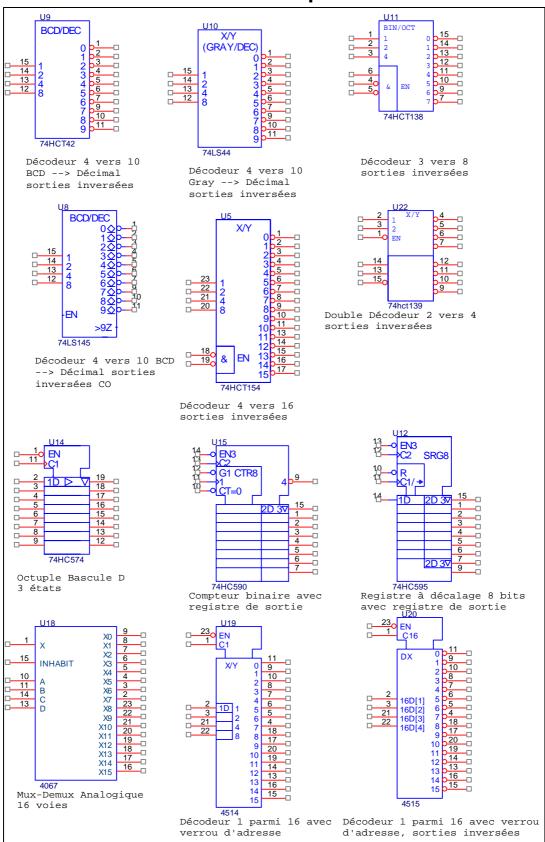

- **Q 4.1)** Donner la capacité mémoire de  $Z_{13}$  et  $Z_{18}$ .

- **Q 4.2)** Identifier les composants qui constituent FS 1.3.

- Q 4.3) Identifier les signaux d'entrée et de sortie en précisant leur rôle.

- **Q 4.4) Donner** les équations des différents signaux de sortie.

- Q 4.5) En déduire la répartition d'adresses mémoire et I/O (donner un tableau de synthèse).

# **4.2** FS 1.6 SAUVEGARDE DES PARAMETRES

- Q 4.6) Donner le composant qui assure cette fonction Donner le type de mémoire Donner sa capacité.

- Q 4.7) Développer sur 4 lignes maximum ce que vous savez de cette technologie.

- Q 4.8) Donner le mode d'accès.

- Q 4.9) Donner le type d'organisation utilisé ici.

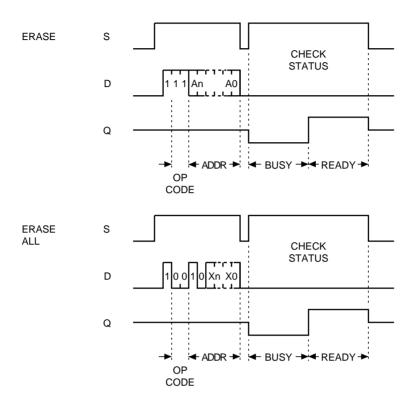

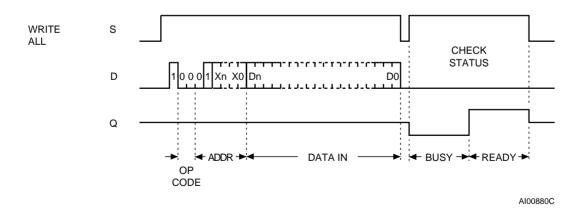

- **Q 4.10)** Donner l'algorithme de lecture d'un octet à une adresse donnée,

On prendra le prototype suivant: *char read\_eeprom(char adr);* où adr est l'adresse de la case mémoire à lire. On nomme **C** l'horloge, **S** la broche de sélection, **D** la broche de donnée entrante, **Q** la broche de donnée sortante.

Dans le texte on nommera PortD le port sur lequel est connecté l'EPROM.

| Q      | S      | С      | D      |

|--------|--------|--------|--------|

| $PD_3$ | $PD_2$ | $PD_1$ | $PD_0$ |

Q 4.11) Justifier la non utilisation du "C" bus du microcontrôleur pour dialoguer avec l'EEPROM.

# 5 CINQUIEME PARTIE PROCESS AUDIO (FP 2)

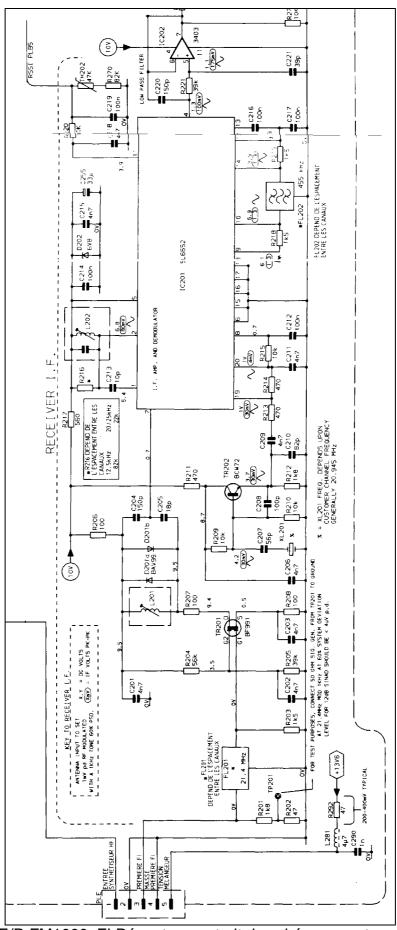

## **5.1** Chaine Reception (FS 2.1)

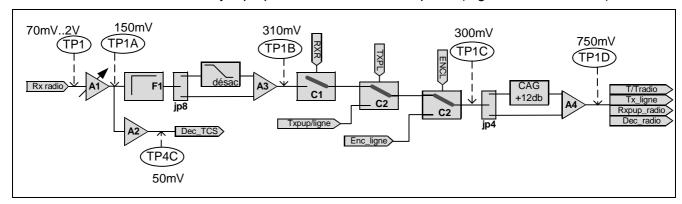

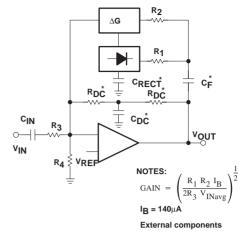

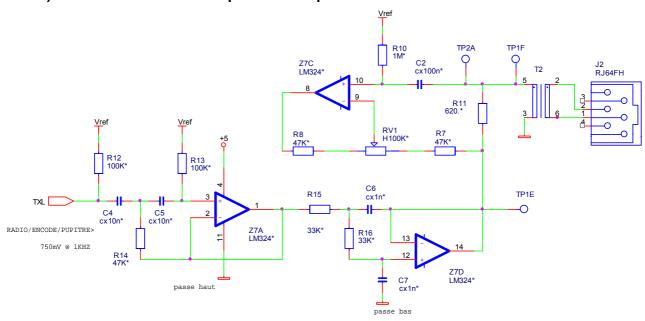

Le constructeur donne un synoptique de la chaîne de réception. (Figure 5.1 ci-dessous) :

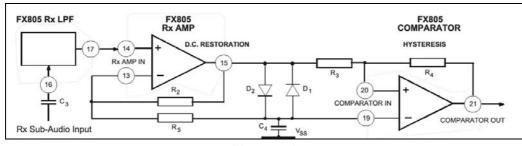

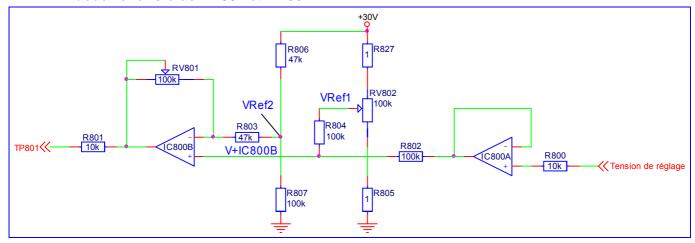

Figure 5.1

- **Q 5.1)** Identifier les composants qui composent les différents éléments de ce synoptique. (voir les schémas structurels des figures 3, 4 et 5 du dossier technique « schémas »). Compléter le tableau dans le dossier réponse.

- **Q 5.2)** Donner l'expression de  $V_{TP1A}$  en fonction de  $V_{TP1}$  et  $V_{Ref.}$

- **Q 5.3)** En **déduire** la ou les fréquences caractéristiques et conclure sur le rôle de C<sub>38</sub>.

- **Q 5.4) Donner** alors une expression simplifiée de  $v_{TP1A}$  en fonction  $v_{TP1}$  dans la bande utile du signal.

- **Q 5.5)** Justifier la valeur de  $R_{V4}$  en tenant compte des valeurs en TP1 et TP1A préconisées par le constructeur.

- **Q 5.6)** Donner le rôle de  $V_{REF}$ .

Le signal destiné au décodeur TCS ne subit pas de filtrage par F1, mais est simplement amplifié par A2.

- Q 5.7) Justifier l'absence de condensateur de couplage entre A1 et A2.

- **Q 5.8)** Justifier la valeur de  $C_{10}$ .

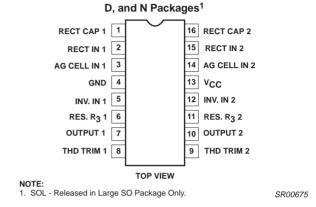

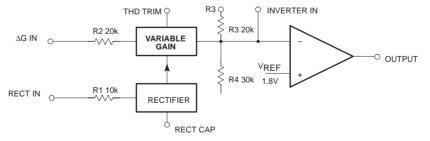

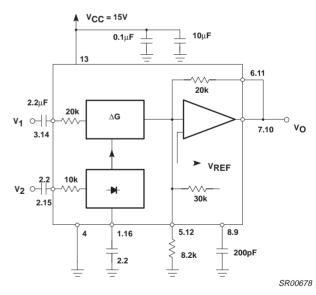

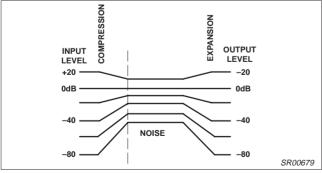

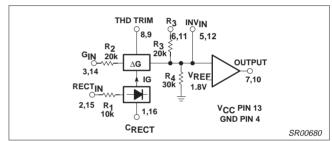

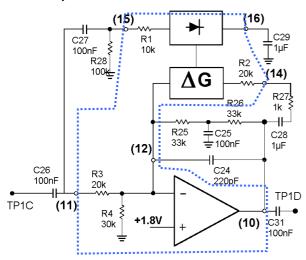

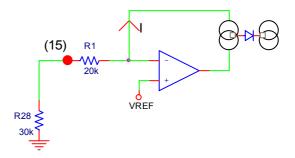

- 5.2 CONTROLE AUTOMATIQUE DE GAIN

On supposera dans les questions qui suivent que le cavalier JP<sub>4</sub> est en position 1.

- Q 5.9) Redessiner le schéma en faisant apparaître le diagramme interne du composant.

- **Q 5.10)** *Préciser* quel le type de fonctionnement utilisé pour ce circuit intégré (compresseur ou expanseur).

EXTRACTION DE L'AMPLITUDE (redresseur/moyenneur)

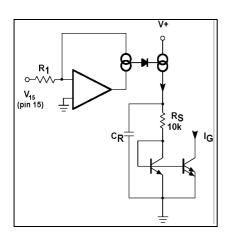

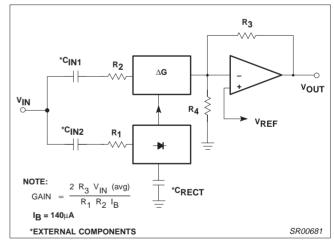

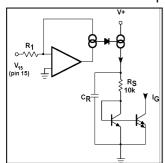

Le constructeur donne pour le redresseur/moyenneur le schéma de principe simplifié suivant :

La documentation précise que le potentiel de la borne non inverseuse de l'AOP est en réalité reliée à  $V_{REF} = 1.8 \text{ V}$ , il s'agit d'un schéma pour les variations de  $V_{15}$ , puisqu'on aura pris soin de mettre une capacité de liaison pour aligner le potentiel continu de  $V_{15}$  à  $V_{REF}$ .

Symbolise un miroir de courant avec redressement double alternance.

- **Q 5.11) Donner** l'expression du courant dans  $R_S(I_{RS}(p))$

- **Q 5.12)** En **déduire** que pour une constante de temps  $R_SC_R$  correctement calculée  $I_{RS} = \frac{|V_{15}|_{moy}}{R_1}$ . En **déduire** l'expression de  $I_G$ .

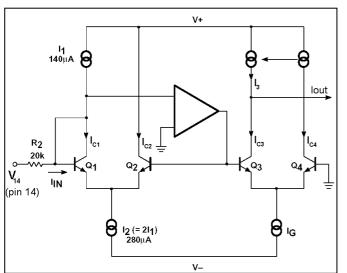

#### **CELLULE A GAIN VARIABLE**

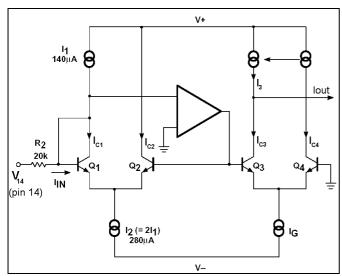

La cellule à gain variable est commandée par le courant  $I_G$  calculé ci-dessus. Le constructeur donne un schéma de principe simplifié de cette cellule :

Même remarque que précédemment concernant le potentiel de référence ( $\frac{1}{=} \Leftrightarrow V_{REF}$ ) L'AOP permet de forcer une variation linéaire de courant entre  $Q_1$  et  $Q_2$ .

- **Q 5.13)** *Montrer* que  $I_{OUT} = \frac{V_{14}}{R_2} \frac{I_G}{I_1}$ .

- **Q 5.14)** Montrer l'influence de  $R_{27}$  sur l'expression de  $I_{OUT}$ .

- **Q 5.15)** En supposant que la résistance R<sub>28</sub> n'est pas connectée, **montrer** que le gain de l'ensemble est :

$$G = \frac{v_{RXO}}{v_{RXI}} = \frac{V_{RXO\;eff}}{V_{RXI\;eff}} = \frac{1}{R_3} \times \frac{R_2 R_1 I_1}{2(|v_{RXI}|_{moy})}.$$

En **déduire** que pour un signal  $V_{RXI}$  sinusoïdal la valeur efficace de  $V_{RXO}$  est constante. **Donner** sa valeur numérique.

Dans le schéma, on a introduit entre la borne 15 et la masse une résistance R<sub>28</sub>.

- **Q 5.16)** Montrer que cette résistance introduit un offset sur le courant  $I_{R1}$  égal à  $-\frac{V_{REF}}{R_1 + R_{28}}$ .

- **Q 5.17)** En **déduire** l'influence sur  $I_G$  puis sur l'ensemble du dispositif CAG. **Donner** le rôle de  $R_{28}$ .

- **5.3** FS 2.3 INTERFACE LIGNE

On se placera dans le cas d'une utilisation simplex, mode TX direct et interface ligne interne.

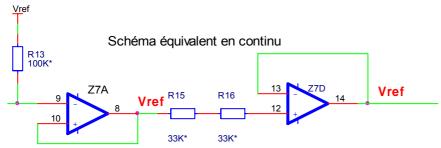

- Q 5.18) Donner un schéma équivalent simplifié entre TP1E et TXL.

- **Q 5.19) Donner** l'expression littérale du gain  $\frac{V_{TP1E}}{V_{TXI}}$

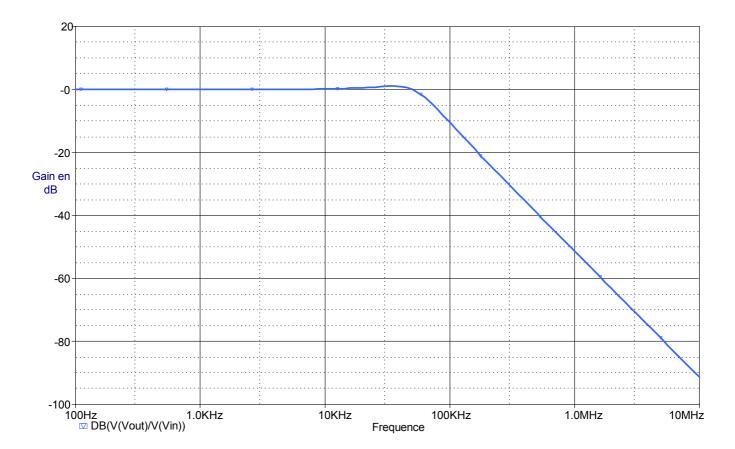

- Q 5.20) Préciser le type de filtre obtenu. Donner les fréquences caractéristiques.

- **Q 5.21)** Donner les valeurs des potentiels continus en sortie de  $Z_{7A}$  et  $Z_{7D}$ .

On supposera l'impédance de ligne égale à 600  $\Omega$  et les transformateurs de ligne parfaits.

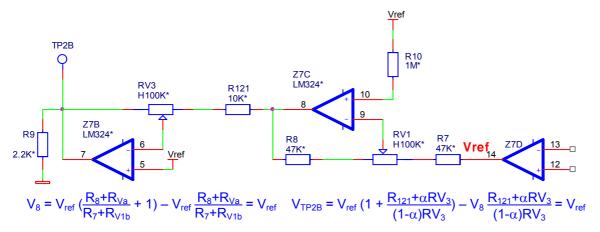

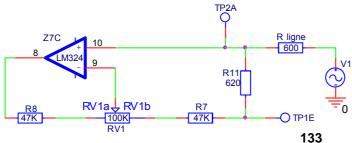

- **Q 5.22)** Analyser la structure autour de  $Z_{7C}$  en continu et **donner** la valeur du potentiel continu en  $S_2$ .

- **Q 5.23) Donner** l'expression littérale de  $v_{S1}$  en fonction de  $v_{TP1E}$  et  $v_{ligne}$ . (on notera  $R_{V1a}$  et  $R_{V1b}$  les valeurs de  $R_{V1}$  de part et d'autre du curseur).

La documentation de SYSTEL indique que « le rapport entre le signal Rx\_ligne et le retour doit être au moins de 20 dB ».

- **Q 5.24) Donner** le réglage de R<sub>V1</sub> pour respecter cette consigne dans les conditions énoncées cidessus.

- Q 5.25) Préciser l'influence éventuelle des caractéristiques du transformateur.

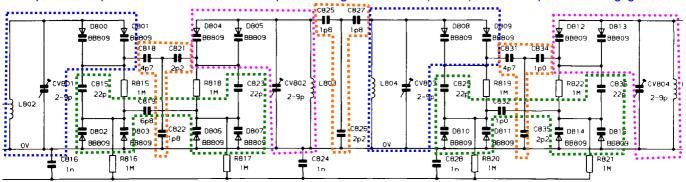

#### 6 SIXIEME PARTIE FP3 ENCODAGE/ DECODAGE

La fonction FP3 assure les codages et décodage de 3 types: numérique FFSK, TCS et 5 Tons.

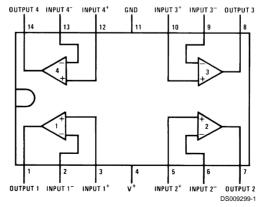

Ces 3 codages sont assurés par des circuits de la même famille: le FX803 (5 tons), le FX805 (TCS) et le FX809 (FFSK). Ils sont connectés à FP1 via le "C" bus, par 3 fils d'interruption et une validation commune aux 3 circuits. Les entrées et sorties BF transitent par FP2 à la réception comme à l'émission.

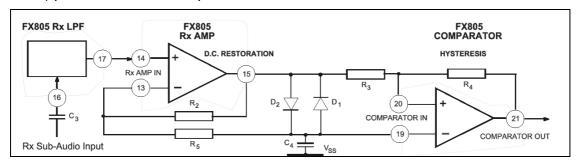

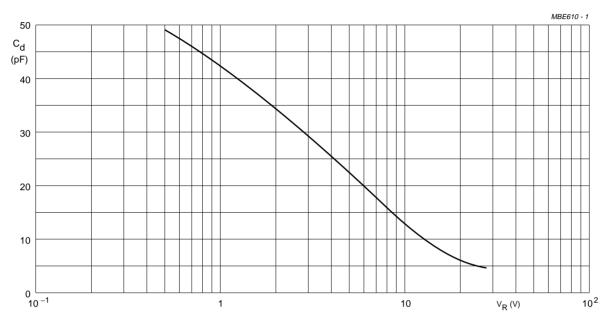

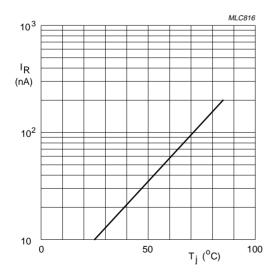

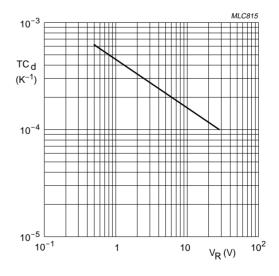

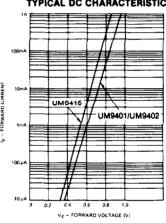

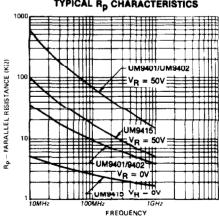

On s'intéressera plus particulièrement au FX805.

#### **6.1** CABLAGE

#### **6.1.1** ADRESSAGE

Les 3 C.I. FX utilisent le même signal de validation CE/1.

**Q 6.1) Donner** les caractéristiques permettant de différencier les 3 circuits.

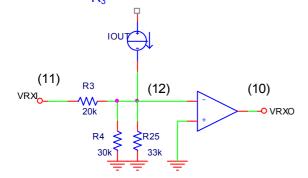

#### **6.1.2** FILTRAGE ET MISE EN FORME

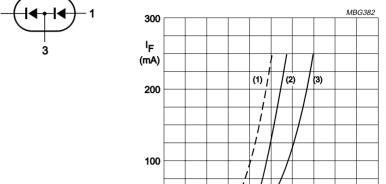

Le signal issu de FP2 (DEC\_TCS) subit un filtrage passe-bas par un filtre intégré au composant (entre 16 et 17) puis est mis en forme par cette structure :

Figure 6.1

Les diodes (CR7A et CR7B) sont des diodes signal classiques. V14 a une composante continue d'environ  $\frac{\text{VCC}}{2}$  et une valeur efficace alternative de 250 mV.

**Q 6.2)** Remplacer les références ci-dessus par celle du schéma (Figure 2 dossier technique « s-chéma »). Etudier le schéma en 2 phases (composante alternative nulle, puis ≠ 0). En déduire le rôle de cette structure et donner la valeur de l'hystérésis.

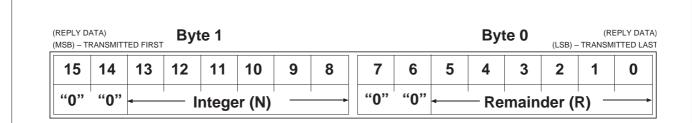

#### **6.2** PROGRAMMATION

Le circuit est configuré pour déclencher une interruption toutes les 122,64 ms, FP1 doit venir lire le code TCS décodé par le circuit. On veut écrire une fonction qui permette de lire et décoder la fréquence reçue. Le prototype de cette fonction sera :

int read\_TCS(void); elle renverra le n° de la fréquence TCS conformément au tableau dans le dossier technique « schémas », figure 7 bis.

On supposera que les fonctions *write\_Cbus\_fx(char byte)* (envoi d'une donnée par le "C" bus) et *char read\_Cbus\_fx(void)* (lecture d'une donnée sur le "C" bus) existent.

**Q 6.3) Donner** l'algorithme de la fonction read\_TCS en vous appuyant sur la documentation du FX805.

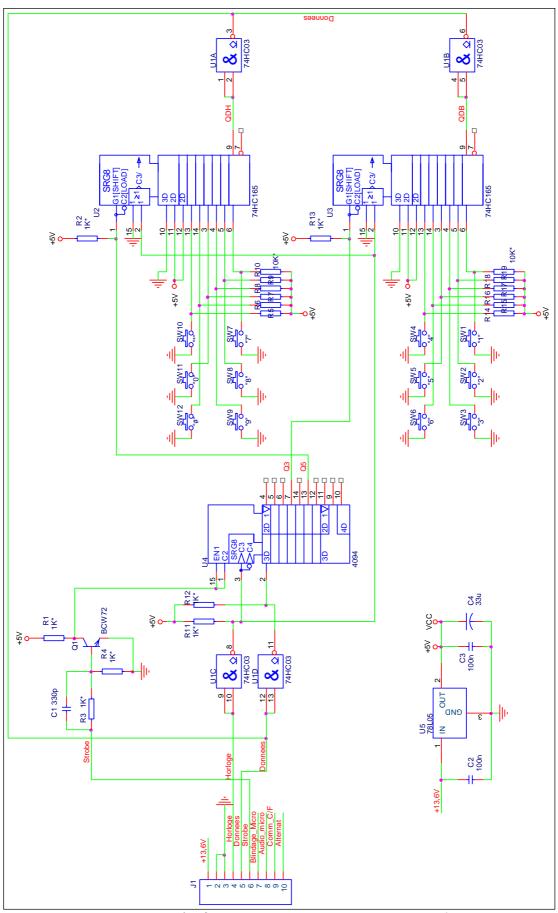

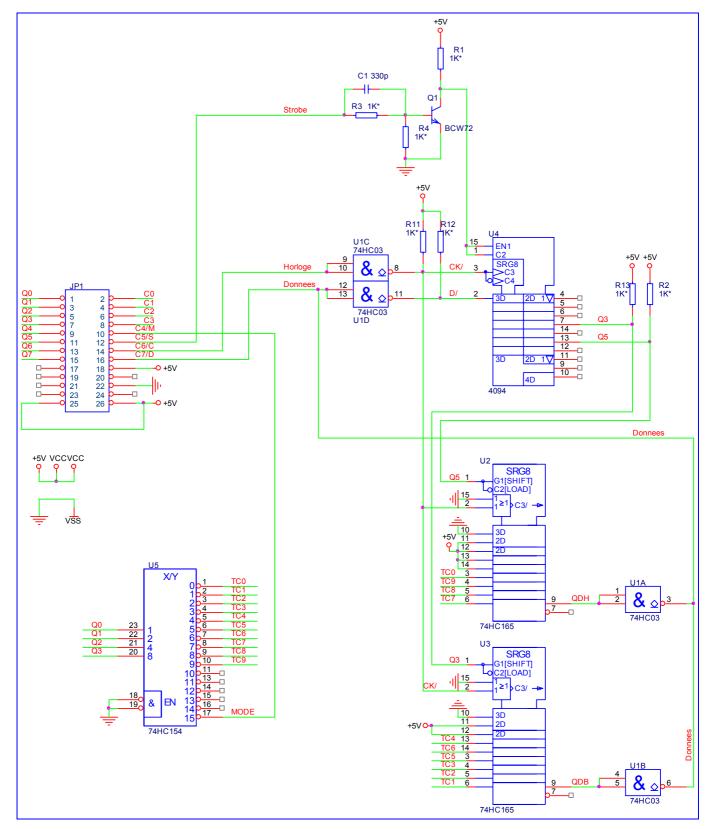

## 7 SEPTIEME PARTIE: INTERFACE CLAVIER

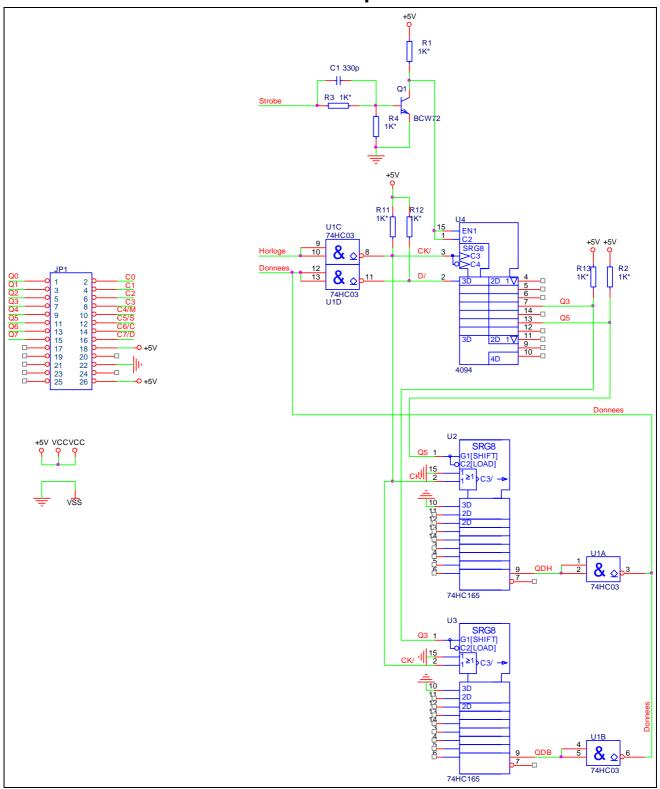

Un boîtier Boxer ou Racer utilise des ensembles émetteur/récepteur Philips de type FM1000. Ces radios sont à priori conçues pour fonctionner seules; la société SYSTEL apporte quelques petites modifications pour pouvoir les intégrer avec la carte VTXCOM (en particulier, sortie des signaux en des points non prévus, modification du harnais de connexion).

Les radios FM1000 disposent normalement d'un clavier à 12 touches pour entrer les numéros de canaux. Dans les boîtiers Racer et Boxer, l'attribution des canaux se fait par programmation ou à la volée par télécommande. Il est donc prévu une option qui permet à la carte VTXCOM de piloter les canaux en émulant le clavier.

On se propose donc d'étudier la structure originale du clavier du FM1000 et de concevoir une solution d'émulation *qui respecte le protocole de lecture* des touches par le FM1000.

Le schéma partiel de l'ensemble microphone clavier à touches est donné figure 10 du dossier technique « schémas » (la partie microphone et interrupteurs n'est pas représentée).

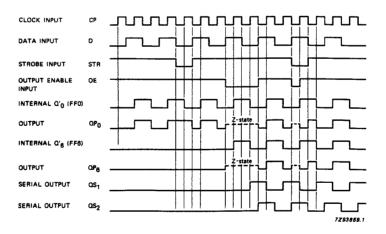

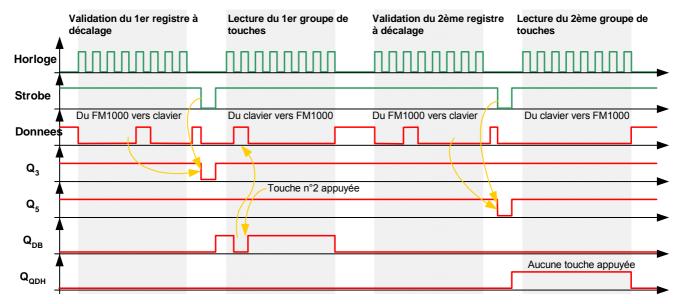

La partie clavier dispose de 3 signaux :

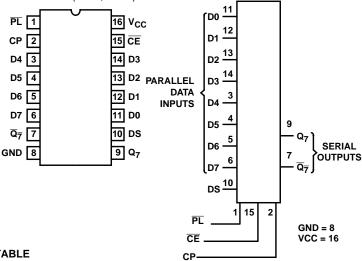

- « Horloge » (unidirectionnelle en provenance du FM1000) qui cadence la lecture ou l'envoi de données,

- « Strobe » (unidirectionnelle en provenance du FM1000) qui valide les données transmises.

- « Donnees » (bidirectionnelle) qui transmet les données en série soit du FM1000 soit vers le FM1000.

- 7.1 ETUDE DU SCHEMA EXISTANT (Figure 10 extrait de l'interface clavier, dossier technique « schémas »)

- **Q 7.1) Donner** la fonction réalisée par l'ensemble  $U_{1A}$  et  $U_{1B}$ .

- Q 7.2) Préciser l'état repos pour la ligne « Donnees » puis pour la ligne « Strobe ».

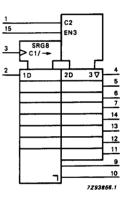

- Q 7.3) Donner le rôle de l'entrée SH/LD (borne 1) du 74HC165.

- **Q 7.4)** Exprimer les conditions de validation du chargement parallèle de  $U_{2}$ , puis de  $U_{3}$ . Utiliser les noms des labels de signaux.

- **Q 7.5) Donner** le rôle des signaux portant les labels Q<sub>3</sub> et Q<sub>5</sub>. **Préciser** s'ils peuvent être actifs simultanément pendant la même phase.

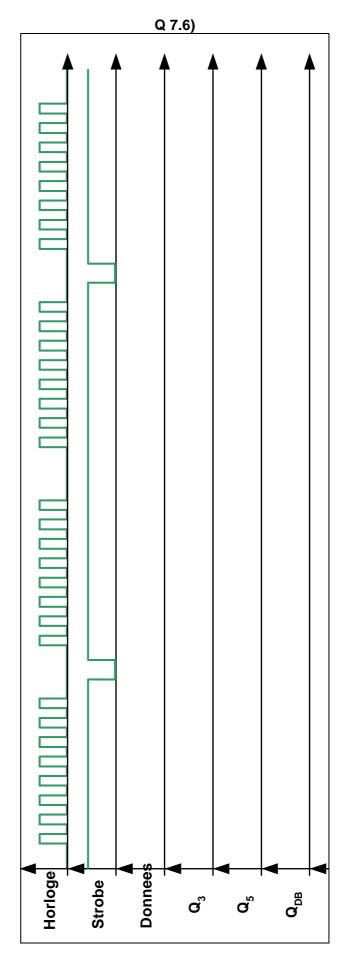

- **Q 7.6)** Compléter le chronogramme relatif à la lecture d'une touche (préciser pour chaque phase le sens du signal « Donnees », en supposant la touche 2 appuyée) (utiliser le Document réponse).

#### 7.2 EMULATION

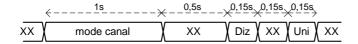

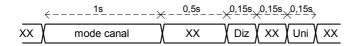

On veut remplacer les touches du clavier par un port I/O de la carte VTXCOM. Pour cela, SYSTEL a choisi d'utiliser les 4 bits de poids faible de FS 5.4. Pour cette application, SYSTEL n'a besoin que des touches 0 à 9 et d'une commande tout ou rien « Mode Canal ».

La carte VTXCOM doit successivement envoyer sur D<sub>3</sub>..D<sub>0</sub>:

Diz: code correspondant à la touche des dizaines

Uni: code correspondant à la touche des unités

Les codes de touche sont \$0 à \$9 pour les touches au numéro correspondant.

**Mode Canal**: code (**\$F**) correspondant au mode canal; ce code est choisi pour être différent d'un code touche **XX**: Codes ne correspondant à aucune touche ni au mode canal (ni **\$0** à **\$9** ni **\$F**)

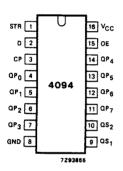

On se propose de trouver une solution permettant de remplacer le clavier.