National Semiconductor

# LMF100 High Performance Dual Switched Capacitor Filter

## **General Description**

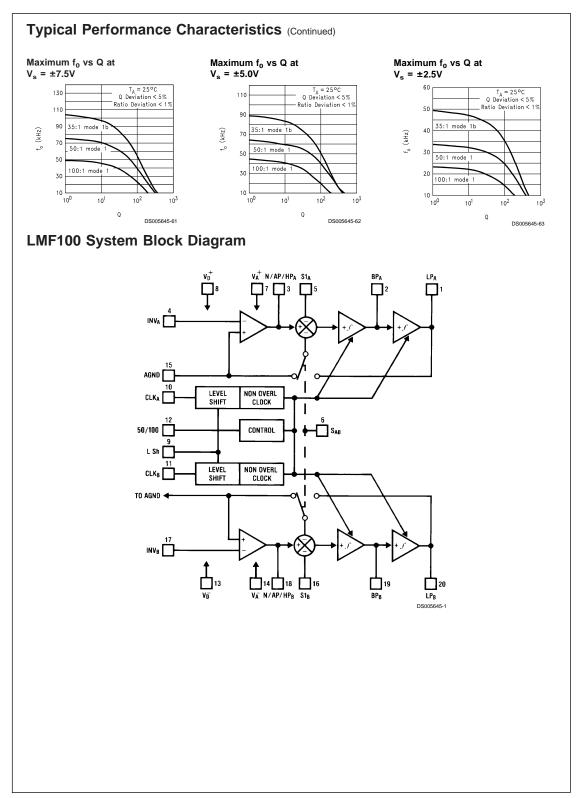

The LMF100 consists of two independent general purpose high performance switched capacitor filters. With an external clock and 2 to 4 resistors, various second-order and first-order filtering functions can be realized by each filter block. Each block has 3 outputs. One output can be configured to perform either an allpass, highpass, or notch function. The other two outputs perform bandpass and lowpass functions. The center frequency of each filter stage is tuned by using an external clock or a combination of a clock and resistor ratio. Up to a 4th-order biquadratic function can be realized with a single LMF100. Higher order filters are implemented by simply cascading additional packages, and all the classical filters (such as Butterworth, Bessel, Elliptic, and Chebyshev) can be realized.

The LMF100 is fabricated on National Semiconductor's high performance analog silicon gate CMOS process,

LMCMOS<sup>™</sup>. This allows for the production of a very low offset, high frequency filter building block. The LMF100 is pin-compatible with the industry standard MF10, but provides greatly improved performance.

#### **Features**

- Wide 4V to 15V power supply range

- Operation up to 100 kHz

- Low offset voltage: typically (50:1 or 100:1 mode): Vos1 = ±5 mV Vos2 = ±15 mV Vos3 = ±15 mV

- Low crosstalk -60 dB

- Clock to center frequency ratio accuracy ±0.2% typical

- $f_0 \ge 0$  range up to 1.8 MHz

- Pin-compatible with MF10

4th Order 100 kHz Butterworth Lowpass Filter +10 4.9 k.0 -10 (Bb) -20 Gain -30 Output LMF100 -40 -50 -60 10 100 1k 10k 100k Frequency (Hz) DS005645-3 DS005645-2 **Connection Diagram** Surface Mount and Dual-In-Line Package LP, LPp BP, BPp N/AP/HP N/AP/HP<sub>B</sub> - INV<sub>B</sub> INV 17 S1 - S1<sub>B</sub> - AGNE - V.-٧٨٩ V<sub>D</sub>+ ۰ ۷<sub>D</sub>-12 -50/100 CLK 11 - CLK<sub>B</sub> DS005645-18 Top View Order Number LMF100CCN or LMF100CIWM See NS Package Number N20A or M20B LMCMOS™ is a trademark of National Semiconductor Corporation.

LMF100 High Performance Dual Switched Capacitor Filter

July 1999

# MACH<sup>®</sup> 4 Family High Performance EE CMOS Programmable Logic With Maximum Ease Of Use

# **DISTINCTIVE CHARACTERISTICS**

- High-performance, EE CMOS CPLD family

- SpeedLocking<sup>™</sup> for guaranteed fixed timing (-7/10/12/15 ns tPD)

- High density

- 1250-10,000 PLD Gates

- 44-208 Pins

- 32-384 Registers

- 32-256 macrocells

- D/T,J-K,S-R Registers and latches

- Synchronous or asynchronous mode

- Programmable polarity

- Reset/preset swapping

- Central, input, and output switch matrices — 100% Routability

- Input and output switch matrices for 100% pin-out retention

- JTAG in-system programmable

- Up to 20 product terms per macrocell, with XOR

- Registered/latched inputs

- Synchronous and asynchronous modes for each macrocell

- Clock generator in each PAL<sup>®</sup> block for programmable clocks, edges in either mode

Individual clock, initialization product terms in asynchronous mode

- Extensive software development support

- Third-party hardware programming support

|             |                      |            |      |                     |                   |                | Commercial              |                           | Industrial           |                         |                         | I <sub>CC</sub> |

|-------------|----------------------|------------|------|---------------------|-------------------|----------------|-------------------------|---------------------------|----------------------|-------------------------|-------------------------|-----------------|

| Device      | Package              | Macrocells | I/Os | Dedicated<br>Inputs | Output<br>Enables | Flip-<br>Flops | t <sub>PD</sub><br>(ns) | f <sub>CNT</sub><br>(MHz) | t <sub>PD</sub> (ns) | t <sub>SS</sub><br>(ns) | t <sub>CO</sub><br>(ns) | Static<br>(mA)  |

| M4(LV)-32   | 44 PLCC<br>44 TQFP   | 32         | 32   | 2                   | 32                | 32             | 7.5                     | 133                       | 10                   | 5.5                     | 5.5                     | 35              |

| M4(LV)-64   | 44 PLCC<br>44 TQFP   | 64         | 32   | 2                   | 32                | 96             | 7.5                     | 133                       | 10                   | 5.5                     | 5.5                     | 55              |

| M4(LV)-96   | 100 TQFP             | 96         | 48   | 8                   | 48                | 144            | 7.5                     | 133                       | 10                   | 5.5                     | 5.5                     | 60              |

| M4-96       | 144 PQFP             | 96         | 96   | 6                   | 96                | 96             | 15                      | 66.6                      | NA                   | NA                      | NA                      | 188             |

| M4(LV)-128  | 100 PQFP<br>100 TQFP | 128        | 64   | 6                   | 64                | 192            | 7.5                     | 133                       | 10                   | 5.5                     | 5.5                     | 70              |

| M4(LV)-128N | 84 PLCC              | 128        | 64   | 6                   | 64                | 192            | 7.5                     | 133                       | 10                   | 5.5                     | 5.5                     | 70              |

| M4(LV)-192  | 144 TQFP             | 192        | 96   | 16                  | 96                | 288            | 10                      | 100                       | 12                   | 6                       | 6.5                     | 85              |

| M4(LV)-256  | 208 PQFP             | 256        | 128  | 14                  | 128               | 384            | 10                      | 100                       | 12                   | 6                       | 6.5                     | 100             |

## **PRODUCT SELECTOR GUIDE**

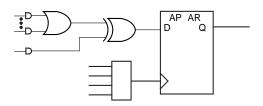

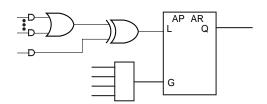

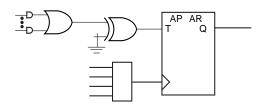

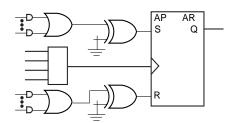

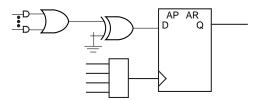

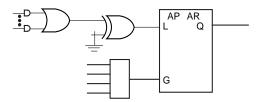

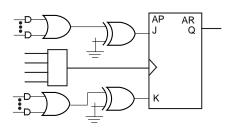

The flip-flop can be configured as a D-type, T-type, J-K, or S-R register or latch. The primary flipflop configurations are shown in Figure 8, although others are possible. Flip-flop functionality is defined in Table 4. Note that a J-K latch is inadvisable, as it will cause oscillation if both J and K inputs are HIGH.

a. D-type with XOR

c. Latch with XOR

e. T-type with programmable T polarity

g. S-R with programmable S and R polarity

b. D-type with programmable D polarity

d. Latch with programmable polarity

f. J-K with programmable J and K polarity

h. Combinatorial with XOR

i. Combinatorial with programmable polarity

17466E-18

Figure 8. Primary Macrocell Configurations

| Configuration   | Input(s) | CLK/LE*                     | Q+             |

|-----------------|----------|-----------------------------|----------------|

|                 | D=X      | 0,1,↓(↑)                    | Q              |

| D-type Register | D=0      | $\uparrow$ ( $\downarrow$ ) | 0              |

|                 | D=1      | $\uparrow\downarrow$        | 1              |

|                 | T=X      | 0, 1, ↓ (↑)                 | Q              |

| T-type Register | T=0      | $\uparrow$ ( $\downarrow$ ) | Q              |

|                 | T=1      | $\uparrow$ ( $\downarrow$ ) | $\overline{Q}$ |

|                 | J=K=X    | 0,1, ↓ (↑)                  | Q              |

|                 | J=0, K=0 | $\uparrow$ ( $\downarrow$ ) | Q              |

| J-K Register    | J=0, K=1 | $\uparrow$ ( $\downarrow$ ) | 0              |

|                 | J=1, K=0 | $\uparrow$ ( $\downarrow$ ) | 1              |

|                 | J=1, K=1 | $\uparrow$ ( $\downarrow$ ) | $\overline{Q}$ |

|                 | S=R=X    | 0,1, O (↓)                  | Q              |

|                 | S=0, R=0 | $\uparrow$ ( $\downarrow$ ) | Q              |

| S-R Register    | S=0, R=1 | $\uparrow$ ( $\downarrow$ ) | 0              |

|                 | S=1, R=0 | $\uparrow$ ( $\downarrow$ ) | 1              |

|                 | S=1, R=1 | $\uparrow$ ( $\downarrow$ ) | Undefined      |

|                 | D=X      | 1 (0)                       | Q              |

| D-type Latch    | D=0      | 0(1)                        | 0              |

|                 | D=1      | 0(1)                        | 1              |

\*Polarity of CLK/LE can be programmed.

Although the macrocell shows only one input to the register, the XOR gate in the logic allocator allows the D-, T-type register to emulate J-K, and S-R behavior. In this case, the available product terms are divided between J and K (or S and R). When configured as J-K, S-R, or T-type, the extra product term must be used on the XOR gate input for flip-flop emulation. In any register type, the polarity of the inputs can be programmed.

The clock input to the flip-flop can select any of the four PAL block clocks in synchronous mode, with the additional choice of either polarity of an individual product term clock in the asynchronous mode.

The initialization circuit depends on the mode. In synchronous mode (Figure 9), asynchronous reset and preset are provided, each driven by a product term common to the entire PAL block.

## Absolute Maximum Ratings (Note 1)

. .

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications. (Note 14)

| Supply Voltage (V <sup>+</sup> – V <sup>-</sup> ) | 16V                   |

|---------------------------------------------------|-----------------------|

| Voltage at Any Pin                                | V <sup>+</sup> + 0.3V |

|                                                   | V <sup>-</sup> – 0.3V |

| Input Current at Any Pin (Note 2)                 | 5 mA                  |

| Package Input Current (Note 2)                    | 20 mA                 |

| Power Dissipation (Note 3)                        | 500 mW                |

| Storage Temperature                               | 150°C                 |

| ESD Susceptability (Note 11)                      | 2000V                 |

| Soldering Information<br>N Package: 10 sec.       | 260°C                 |

| J Package: 10 sec.                         | 300°C |

|--------------------------------------------|-------|

| SO Package:                                |       |

| Vapor Phase (60 sec.)                      | 215°C |

| Infrared (15 sec.)                         | 220°C |

| See AN-450 "Surface Mounting Methods and T |       |

on Product Reliability" (Appendix D) for other methods of soldering surface mount devices.

### **Operating Ratings** (Note 1)

| Temperature Range | $T_{MIN} \le T_A \le T_{MAX}$           |

|-------------------|-----------------------------------------|

| LMF100CCN         | $0^{\circ}C \le T_{A} \le +70^{\circ}C$ |

| LMF100CIWM        | $-40^{\circ}C \le T_A \le +85^{\circ}C$ |

| Supply Voltage    | $4V \leq V^+ - V^- \leq 15V$            |

#### **Electrical Characteristics**

The following specifications apply for Mode 1, Q = 10 ( $R_1 = R_3 = 100k$ ,  $R_2 = 10k$ ), V<sup>+</sup> = +5V and V<sup>-</sup> = -5V unless otherwise specified. **Boldface limits apply for T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits  $T_A = T_J = 25^{\circ}C$ .

|                                  |                                         |         |                                                                                                                   |                          | LMF100CC | N                           | LMF100CIWM                   |                     |                             |                              |       |

|----------------------------------|-----------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------|--------------------------|----------|-----------------------------|------------------------------|---------------------|-----------------------------|------------------------------|-------|

| Symbol                           | Parameter                               |         | Condition                                                                                                         | Conditions Ty<br>(N      |          | Tested<br>Limit<br>(Note 9) | Design<br>Limit<br>(Note 10) | Typical<br>(Note 8) | Tested<br>Limit<br>(Note 9) | Design<br>Limit<br>(Note 10) | Units |

| ls                               | Maximum Supply Cu                       | urrent  | f <sub>CLK</sub> = 250 kHz                                                                                        | <sub>CLK</sub> = 250 kHz |          | 13                          | 13                           | 9                   | 13                          |                              | mA    |

|                                  |                                         |         | No Input Signal                                                                                                   |                          |          |                             |                              |                     |                             |                              |       |

| f <sub>0</sub>                   | Center Frequency                        | MIN     |                                                                                                                   |                          | 0.1      |                             |                              | 0.1                 |                             |                              | Hz    |

|                                  | Range                                   | MAX     |                                                                                                                   |                          | 100      |                             |                              | 100                 |                             |                              | kHz   |

| f <sub>CLK</sub>                 | Clock Frequency                         | MIN     |                                                                                                                   |                          | 5.0      |                             |                              | 5.0                 |                             |                              | Hz    |

|                                  | Range                                   | MAX     |                                                                                                                   |                          | 3.5      |                             |                              | 3.5                 |                             |                              | MHz   |

| f <sub>CLK</sub> /f <sub>0</sub> | Clock to Center Free<br>Ratio Deviation | quency  | $V_{Pin12}$ = 5V or 0V<br>f <sub>CLK</sub> = 1 MHz                                                                |                          | ±0.2     | ±0.8                        | ±0.8                         | ±0.2                | ±0.8                        |                              | %     |

| $\frac{\Delta Q}{Q}$             |                                         |         | $\begin{array}{l} Q = 10, \mbox{ Mode 1} \\ V_{Pin12} = 5V \mbox{ or } 0V \\ f_{CLK} = 1 \mbox{ MHz} \end{array}$ |                          | ±0.5     | ±5                          | ±6                           | ±0.5                | ±6                          |                              | %     |

| H <sub>OBP</sub>                 | Bandpass Gain at fo                     |         | f <sub>CLK</sub> = 1 MHz                                                                                          |                          | 0        | ±0.4                        | ±0.4                         | 0                   | ±0.4                        |                              | dB    |

| HOLP                             | DC Lowpass Gain                         |         | $R_1 = R_2 = 10k$                                                                                                 |                          | 0        | ±0.2                        | ±0.2                         | 0                   | ±0.2                        |                              | dB    |

|                                  |                                         |         | f <sub>CLK</sub> = 250 kHz                                                                                        |                          |          |                             |                              |                     |                             |                              |       |

| V <sub>OS1</sub>                 | DC Offset Voltage (I                    | Note 5) | f <sub>CLK</sub> = 250 kHz                                                                                        |                          | ±5.0     | ±15                         | ±15                          | ±5.0                | ±15                         |                              | mV    |

| V <sub>OS2</sub>                 | DC Offset Voltage (I                    | Note 5) | f <sub>CLK</sub> = 250 kHz                                                                                        | $S_{A/B} = V^+$          | ±30      | ±80                         | ±80                          | ±30                 | ±80                         |                              | mV    |

|                                  |                                         |         |                                                                                                                   | $S_{A/B} = V^-$          | ±15      | ±70                         | ±70                          | ±15                 | ±70                         |                              | mV    |

| V <sub>OS3</sub>                 | DC Offset Voltage (I                    | Note 5) | f <sub>CLK</sub> = 250 kHz                                                                                        |                          | ±15      | ±40                         | ±60                          | ±15                 | ±60                         |                              | mV    |

|                                  | Crosstalk (Note 6)                      |         | A Side to B Side or                                                                                               |                          | -60      |                             |                              | -60                 |                             |                              | dB    |

|                                  |                                         |         | B Side to A Side                                                                                                  |                          | -00      |                             |                              | -60                 |                             |                              | UD    |

|                                  | Output Noise (Note                      | 12)     | f <sub>CLK</sub> = 250 kHz                                                                                        | N                        | 40       |                             |                              | 40                  |                             |                              |       |

|                                  |                                         |         | 20 kHz Bandwidth                                                                                                  | BP                       | 320      |                             |                              | 320                 |                             |                              | μV    |

|                                  |                                         |         | 100:1 Mode                                                                                                        | LP                       | 300      |                             |                              | 300                 |                             |                              | 1     |

|                                  | Clock Feedthrough<br>(Note 13)          |         | f <sub>CLK</sub> = 250 kHz 100:                                                                                   | 1 Mode                   | 6        |                             |                              | 6                   |                             |                              | mV    |

| V <sub>OUT</sub>                 | Minimum Output                          |         | R <sub>L</sub> = 5k                                                                                               |                          | +4.0     | ±3.8                        | ±3.7                         | +4.0                | ±3.7                        |                              | v     |

|                                  | Voltage Swing                           |         | (All Outputs)                                                                                                     |                          | -4.7     | 13.0                        | ±3.7                         | -4.7                | ±3.7                        |                              | v     |

|                                  |                                         |         | R <sub>L</sub> = 3.5k                                                                                             |                          | +3.9     |                             |                              | +3.9                |                             |                              | v     |

|                                  |                                         |         | (All Outputs)                                                                                                     |                          | -4.6     |                             |                              | -4.6                |                             |                              | v     |

| GBW                              | Op Amp Gain BW P                        | roduct  |                                                                                                                   |                          | 5        |                             |                              | 5                   |                             |                              | MHz   |

| SR                               | Op Amp Slew Rate                        |         |                                                                                                                   |                          | 20       |                             |                              | 20                  |                             |                              | V/µs  |

| I <sub>sc</sub>                  | Maximum Output<br>Short                 | Source  | (All Outputs)                                                                                                     |                          | 12       |                             |                              | 12                  |                             |                              | mA    |

|                                  | Circuit Current<br>(Note 7)             | Sink    |                                                                                                                   |                          | 45       |                             |                              | 45                  |                             |                              | mA    |

The following specifications apply for Mode 1, Q = 10 ( $R_1 = R_3 = 100k$ ,  $R_2 = 10k$ ), V<sup>+</sup> = +5V and V<sup>-</sup> = -5V unless otherwise specified. Boldface limits apply for  $T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25^{\circ}C$ .

|                 |                              |            |                     | LMF100CC                    | N                            | L                   | MF100CIW                    | /M                           |       |

|-----------------|------------------------------|------------|---------------------|-----------------------------|------------------------------|---------------------|-----------------------------|------------------------------|-------|

| Symbol          | Parameter                    | Conditions | Typical<br>(Note 8) | Tested<br>Limit<br>(Note 9) | Design<br>Limit<br>(Note 10) | Typical<br>(Note 8) | Tested<br>Limit<br>(Note 9) | Design<br>Limit<br>(Note 10) | Units |

| I <sub>IN</sub> | Input Current on Pins: 4, 5, |            |                     | 10                          |                              |                     | 10                          |                              | μΑ    |

|                 | 6, 9, 10, 11, 12, 16, 17     |            |                     |                             |                              |                     |                             |                              |       |

#### **Electrical Characteristics**

The following specifications apply for Mode 1, Q = 10 ( $R_1 = R_3 = 100k$ ,  $R_2 = 10k$ ), V<sup>+</sup> = +2.50V and V<sup>-</sup> = -2.50V unless otherwise specified. **Boldface limits apply for T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits  $T_A = T_J = 25^{\circ}C$ .

|                                  |                                        |          |                                                             |                                   |                     |                             | N                               | L                   |                             |                                 |       |

|----------------------------------|----------------------------------------|----------|-------------------------------------------------------------|-----------------------------------|---------------------|-----------------------------|---------------------------------|---------------------|-----------------------------|---------------------------------|-------|

| Symbol                           | Parameter                              |          |                                                             |                                   | Typical<br>(Note 8) | Tested<br>Limit<br>(Note 9) | Design<br>Limit<br>(Note<br>10) | Typical<br>(Note 8) | Tested<br>Limit<br>(Note 9) | Design<br>Limit<br>(Note<br>10) | Units |

| ls                               | Maximum Supply<br>Current              |          | f <sub>CLK</sub> = 250 kHz<br>No Input Signal               |                                   | 8                   | 12                          | 12                              | 8                   | 12                          |                                 | mA    |

| f <sub>0</sub>                   | Center Frequency                       | MIN      |                                                             |                                   | 0.1                 |                             |                                 | 0.1                 |                             |                                 | Hz    |

|                                  | Range                                  | MAX      |                                                             |                                   | 50                  |                             |                                 | 50                  |                             |                                 | kHz   |

| f <sub>CLK</sub>                 | Clock Frequency                        | MIN      |                                                             |                                   | 5.0                 |                             |                                 | 5.0                 |                             |                                 | Hz    |

|                                  | Range                                  | MAX      |                                                             |                                   | 1.5                 |                             |                                 | 1.5                 |                             |                                 | MHz   |

| f <sub>CLK</sub> /f <sub>0</sub> | Clock to Center<br>Frequency Ratio Dev | iation   | V <sub>Pin12</sub> = 2.5V or 0V<br>f <sub>CLK</sub> = 1 MHz | V                                 | ±0.2                | ±1                          | ±1                              | ±0.2                | ±1                          |                                 | %     |

| ΔQ                               | Q Error (MAX)                          |          | Q = 10, Mode 1                                              |                                   |                     |                             |                                 |                     |                             |                                 |       |

| Q                                | (Note 4)                               | ote 4)   |                                                             |                                   | ±0.5                | ±5                          | ±8                              | ±0.5                | ±8                          |                                 | %     |

| H <sub>OBP</sub>                 | Bandpass Gain at f <sub>0</sub>        |          | f <sub>CLK</sub> = 1 MHz                                    |                                   | 0                   | ±0.4                        | ±0.5                            | 0                   | ±0.5                        |                                 | dB    |

| H <sub>OLP</sub>                 | DC Lowpass Gain                        |          | $R_1 = R_2 = 10k$<br>$f_{CLK} = 250 \text{ kHz}$            |                                   | 0                   | ±0.2                        | ±0.2                            | 0                   | ±0.2                        |                                 | dB    |

| V <sub>OS1</sub>                 | DC Offset Voltage (N                   | ote 5)   | f <sub>CLK</sub> = 250 kHz                                  | f <sub>CLK</sub> = 250 kHz        |                     | ±15                         | ±15                             | ±5.0                | ±15                         |                                 | mV    |

| V <sub>OS2</sub>                 | 2 DC Offset Voltage (Note 5)           |          | f <sub>CLK</sub> = 250 kHz                                  | S <sub>A/B</sub> = V <sup>+</sup> | ±20                 | ±60                         | ±60                             | ±20                 | ±60                         |                                 | mV    |

|                                  |                                        |          |                                                             | S <sub>A/B</sub> = V <sup>-</sup> | ±10                 | ±50                         | ±60                             | ±10                 | ±60                         |                                 | mV    |

| V <sub>OS3</sub>                 | DC Offset Voltage (N                   | ote 5)   | f <sub>CLK</sub> = 250 kHz                                  |                                   | ±10                 | ±25                         | ±30                             | ±10                 | ±30                         |                                 | mV    |

|                                  | Crosstalk (Note 6)                     |          | A Side to B Side o<br>B Side to A Side                      | r                                 | -65                 |                             |                                 | -65                 |                             |                                 | dB    |

|                                  | Output Noise (Note 1                   | 2)       | f <sub>CLK</sub> = 250 kHz                                  | N                                 | 25                  |                             |                                 | 25                  |                             |                                 |       |

|                                  |                                        |          | 20 kHz Bandwidth                                            | BP                                | 250                 |                             |                                 | 250                 |                             |                                 | μV    |

|                                  |                                        |          | 100:1 Mode                                                  | LP                                | 220                 |                             |                                 | 220                 |                             |                                 |       |

|                                  | Clock Feedthrough (I                   | Note 13) | f <sub>CLK</sub> = 250 kHz 100                              | 0:1 Mode                          | 2                   |                             |                                 | 2                   |                             |                                 | mV    |

| V <sub>OUT</sub>                 | Minimum Output<br>Voltage Swing        |          | R <sub>L</sub> = 5k<br>(All Outputs)                        |                                   | +1.6<br>-2.2        | ±1.5                        | ±1.4                            | +1.6<br>-2.2        | ±1.4                        |                                 | V     |

|                                  |                                        |          | R <sub>L</sub> = 3.5k                                       |                                   | +1.5                |                             |                                 | +1.5                |                             |                                 | V     |

|                                  |                                        |          | (All outputs)                                               |                                   | -2.1                |                             |                                 | -2.1                |                             |                                 |       |

| GBW                              | Op Amp Gain BW Pr                      | oduct    |                                                             |                                   | 5                   |                             |                                 | 5                   |                             |                                 | MHz   |

| SR                               | Op Amp Slew Rate                       |          |                                                             |                                   | 18                  |                             |                                 | 18                  |                             |                                 | V/µs  |

| I <sub>sc</sub>                  | Maximum Output<br>Short Circuit        | Source   | (All Outputs)                                               |                                   | 10                  |                             |                                 | 10                  |                             |                                 | mA    |

|                                  | Current (Note 7)                       | Sink     |                                                             |                                   | 20                  |                             |                                 | 20                  |                             |                                 | mA    |

| Logic | Input | Characteristics |

|-------|-------|-----------------|

|-------|-------|-----------------|

. .

**Boldface limits apply for T\_{MIN} to T\_{MAX};** all other limits  $T_A = T_J = 25^{\circ}C$ .

|               |                 |                                                 |          | LMF100CCM | 1         | I        | LMF100CIW | М         |       |

|---------------|-----------------|-------------------------------------------------|----------|-----------|-----------|----------|-----------|-----------|-------|

| Parameter     |                 | Conditions                                      | Typical  | Tested    | Design    | Typical  | Tested    | Design    | Units |

| Par           | ameter          | Conditions                                      | (Note 8) | Limit     | Limit     | (Note 8) | Limit     | Limit     | Units |

|               |                 |                                                 |          | (Note 9)  | (Note 10) |          | (Note 9)  | (Note 10) |       |

| CMOS Clock    | MIN Logical "1" | $V^+ = +5V, V^- = -5V,$                         |          | +3.0      | +3.0      |          | +3.0      |           | V     |

| Input Voltage | MAX Logical "0" | V <sub>LSh</sub> = 0V                           |          | -3.0      | -3.0      |          | -3.0      |           | V     |

|               | MIN Logical "1" | V <sup>+</sup> = +10V, V <sup>-</sup> = 0V,     |          | +8.0      | +8.0      |          | +8.0      |           | V     |

|               | MAX Logical "0" | V <sub>LSh</sub> = +5V                          |          | +2.0      | +2.0      |          | +2.0      |           | V     |

| TTL Clock     | MIN Logical "1" | $V^+ = +5V, V^- = -5V,$                         |          | +2.0      | +2.0      |          | +2.0      |           | V     |

| Input Voltage | MAX Logical "0" | V <sub>LSh</sub> = 0V                           |          | +0.8      | +0.8      |          | +0.8      |           | V     |

|               | MIN Logical "1" | V <sup>+</sup> = +10V, V <sup>-</sup> = 0V,     |          | +2.0      | +2.0      |          | +2.0      |           | V     |

|               | MAX Logical "0" | V <sub>LSh</sub> = 0V                           |          | +0.8      | +0.8      |          | +0.8      |           | V     |

| CMOS Clock    | MIN Logical "1" | V <sup>+</sup> = +2.5V, V <sup>-</sup> = -2.5V, |          | +1.5      | +1.5      |          | +1.5      |           | V     |

| Input Voltage | MAX Logical "0" | V <sub>LSh</sub> = 0V                           |          | -1.5      | -1.5      |          | -1.5      |           | V     |

|               | MIN Logical "1" | V <sup>+</sup> = +5V, V <sup>-</sup> = 0V,      |          | +4.0      | +4.0      |          | +4.0      |           | V     |

|               | MAX Logical "0" | V <sub>LSh</sub> = +2.5V                        |          | +1.0      | +1.0      |          | +1.0      |           | V     |

| TTL Clock     | MIN Logical "1" | $V^+ = +5V, V^- = 0V,$                          |          | +2.0      | +2.0      |          | +2.0      |           | V     |

| Input Voltage | MAX Logical "0" | $V_{LSh} = 0V, V_{D}^{+} = 0V$                  |          | +0.8      | +0.8      |          | +0.8      |           | V     |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional. These ratings do not guarantee specific performance limits, however. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: When the input voltage  $(V_{|N})$  at any pin exceeds the power supply rails  $(V_{|N} < V^- \text{ or } V_{|N} > V^+)$  the absolute value of current at that pin should be limited to 5 mA or less. The sum of the currents at all pins that are driven beyond the power supply voltages should not exceed 20 mA.

Note 3: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable power dissipation at any temperature is  $P_D = (T_{JMAX} - T_A)/\theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is lower. For this device,  $T_{JMAX} = 125^{\circ}$ C, and the typical junction-to-ambient thermal resistance of the LMF100CIN when board mounted is 55°C/W. For the LMF100CIWM this number is 66°C/W.

Note 4: The accuracy of the Q value is a function of the center frequency (f<sub>0</sub>). This is illustrated in the curves under the heading "Typical Peformance Characteristics". Note 5: V<sub>051</sub>, V<sub>052</sub>, and V<sub>053</sub> refer to the internal offsets as discussed in the Applications Information section 3.4.

Note 6: Crosstalk between the internal filter sections is measured by applying a 1  $V_{RMS}$  10 kHz signal to one bandpass filter section input and grounding the input of the other bandpass filter section. The crosstalk is the ratio between the output of the grounded filter section and the 1  $V_{RMS}$  input signal of the other section. Note 7: The short circuit source current is measured by forcing the output that is being tested to its maximum positive voltage swing and then shorting that output

to the negative supply. The short circuit sink current is measured by forcing the output that is being tested to its maximum negative voltage swing and then shorting that output to the positive supply. These are the worst case conditions.

Note 8: Typicals are at 25°C and represent most likely parametric norm.

Note 9: Tested limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 10: Design limits are guaranteed to National's AOQL (Average Outgoing Quality Level) but are not 100% tested.

Note 11: Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor.

Note 12: In 50:1 mode the output noise is 3 dB higher.

Note 13: In 50:1 mode the clock feedthrough is 6 dB higher.

Note 14: A military RETS specification is available upon request.

| Pin Descript                                                       | ions                                                                                                                                                                                                                                                                                                                                             | LSh(9)                                       | Level shift pin. This is used to                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LP(1,20),<br>BP(2,19),<br>N/AP/HP(3,18)                            | The second order lowpass, bandpass and notch/allpass/highpass outputs. These outputs can typically swing to within 1V of each supply when driving a 5 k $\Omega$ load. For optimum performance, capacitive loading on these outputs should be minimized. For signal frequencies above 15 kHz the capacitance loading should be kept below 30 pF. |                                              | accommodate various clock levels<br>with dual or single supply<br>operation. With dual ±5V supplies<br>and CMOS (±5V) or TTL (0V–5V)<br>clock levels, LSh should be tied to<br>system ground.<br>For 0V–10V single supply<br>operation the AGND pin should be<br>biased at +5V and the LSh pin<br>should be tied to the system<br>ground for TTL clock levels. LSh<br>should be biased at +5V for ±5V<br>CMOS clock levels. |

| NV(4,17)                                                           | The inverting input of the<br>summing opamp of each filter.<br>These are high impedance inputs.<br>The non-inverting input is<br>internally tied to AGND so the<br>opamp can be used only as an<br>inverting amplified                                                                                                                           | CLK(10,11)                                   | The LSh pin is tied to system<br>ground for $\pm 2.5V$ operation. For<br>single 5V operation the LSh and<br>$V_D$ + pins are tied to system<br>ground for TTL clock levels.<br>Clock inputs for the two switched                                                                                                                                                                                                            |

| S1(5,16)                                                           | inverting amplifier.<br>S1 is a signal input pin used in<br>modes 1b, 4, and 5. The input<br>impedance is $1/f_{CLK} \times 1$ pF. The<br>pin should be driven with a source<br>impedance of less than 1 k $\Omega$ . If<br>S1 is not driven with a signal it<br>should be tied to AGND<br>(mid-supply).                                         |                                              | capacitor filter sections. Unipolar<br>or bipolar clock levels may be<br>applied to the CLK inputs<br>according to the programming<br>voltage applied to the LSh pin.<br>The duty cycle of the clock should<br>be close to 50%, especially when<br>clock frequencies above 200 kHz                                                                                                                                          |

| S <sub>A/B</sub> (6)                                               | This pin activates a switch that<br>connects one of the inputs of each<br>filter's second summer either to<br>AGND ( $S_{AVB}$ tied to V <sup>-</sup> ) or to the                                                                                                                                                                                |                                              | are used. This allows the<br>maximum time for the internal<br>opamps to settle, which yields<br>optimum filter performance.                                                                                                                                                                                                                                                                                                 |

|                                                                    | lowpass (LP) output ( $S_{A/B}$ tied to V <sup>+</sup> ). This offers the flexibility needed for configuring the filter in its various modes of operation.                                                                                                                                                                                       | 50/100(12)<br>(Note 15)                      | By tying this pin to V <sup>+</sup> a 50:1 clock<br>to filter center frequency ratio is<br>obtained. Tying this pin at<br>mid-supply (i.e., system ground                                                                                                                                                                                                                                                                   |

| V <sub>A</sub> +(7) (Note 15)                                      | This is both the analog and digital positive supply.                                                                                                                                                                                                                                                                                             |                                              | with dual supplies) or to V <sup>-</sup> allows<br>the filter to operate at a 100:1<br>clock to center frequency ratio.                                                                                                                                                                                                                                                                                                     |

| V <sub>D</sub> <sup>+</sup> (8) (Note 15)                          | This pin needs to be tied to V <sup>+</sup><br>except when the device is to<br>operate on a single 5V supply and<br>a TTL level clock is applied. For<br>5V, TTL operation, $V_D^+$ should be<br>tied to ground (0V).                                                                                                                            | AGND(15)                                     | This is the analog ground pin.<br>This pin should be connected to<br>the system ground for dual supply<br>operation or biased to mid-supply<br>for single supply operation. For a<br>further discussion of mid-supply                                                                                                                                                                                                       |

| V <sub>A</sub> <sup>-</sup> (14), V <sub>D</sub> <sup>-</sup> (13) | Analog and digital negative<br>supplies. $V_A^-$ and $V_D^-$ should be<br>derived from the same source.<br>They have been brought out<br>separately so they can be<br>bypassed by separate capacitors,                                                                                                                                           |                                              | biasing techniques see the<br>Applications Information (Section<br>3.2). For optimum filter<br>performance a "clean" ground<br>must be provided.                                                                                                                                                                                                                                                                            |

|                                                                    | if desired. They can also be tied<br>together externally and bypassed<br>with a single capacitor.                                                                                                                                                                                                                                                | following changes:<br>1. Unlike the MF10, th | is pin-for-pin compatible with the MF10 except for the LMF100 has a single positive supply pin (V <sub>A</sub> +). is a control pin and is not the digital positive supply a                                                                                                                                                                                                                                                |

|                                                                    |                                                                                                                                                                                                                                                                                                                                                  |                                              | e LMF100 does not support the current limiting mode<br>s tied to V <sup>-</sup> the LMF100 will remain in the 100:1 mode                                                                                                                                                                                                                                                                                                    |

#### 1.0 Definitions of Terms

f<sub>CLK</sub>: the frequency of the external clock signal applied to pin 10 or 11

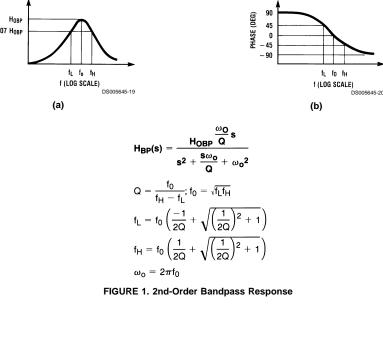

fo: center frequency of the second order function complex pole pair.  $\boldsymbol{f}_0$  is measured at the bandpass outputs of the LMF100, and is the frequency of maximum bandpass gain. (Figure 1).

$f_{notch}$ : the frequency of minimum (ideally zero) gain at the notch outputs.

f<sub>z</sub>: the center frequency of the second order complex zero pair, if any. If  $f_z$  is different from  $f_0$  and if  $\mathsf{Q}_z$  is high, it can be observed as the frequency of a notch at the allpass output. (Figure 13).

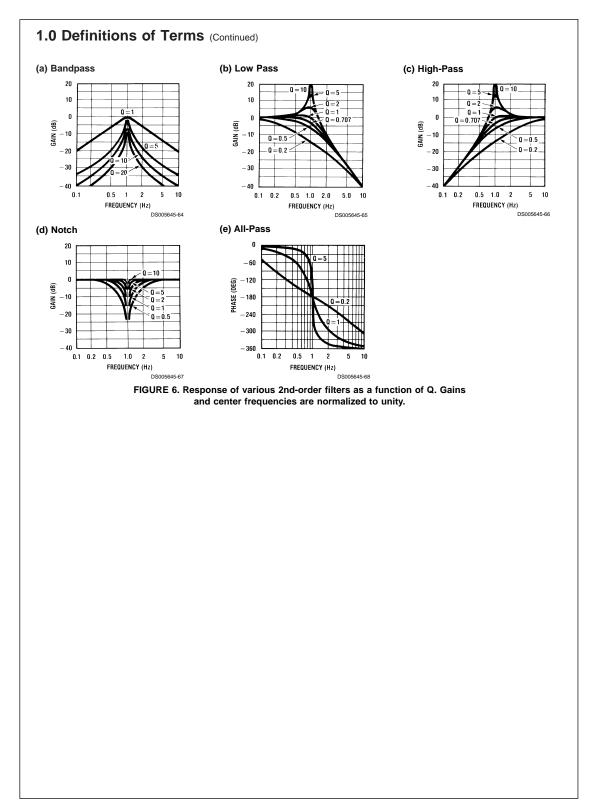

Q: "quality factor" of the 2nd order filter. Q is measured at the bandpass outputs of the LMF100 and is equal to fo divided by the -3 dB bandwidth of the 2nd order bandpass filter (Figure 1). The value of Q determines the shape of the 2nd order filter responses as shown in Figure 6.

Qz: the quality factor of the second order complex zero pair, if any.  $\mathsf{Q}_{\mathsf{Z}}$  is related to the allpass characteristic, which is written:

BAIN (V/V)

$$H_{AP}(s) = \frac{H_{OAP}\left(s^2 - \frac{s\omega_0}{Q_z} + \omega_0^2\right)}{s^2 + \frac{s\omega_0}{Q} + \omega_0^2}$$

where  $Q_Z = Q$  for an all-pass response.

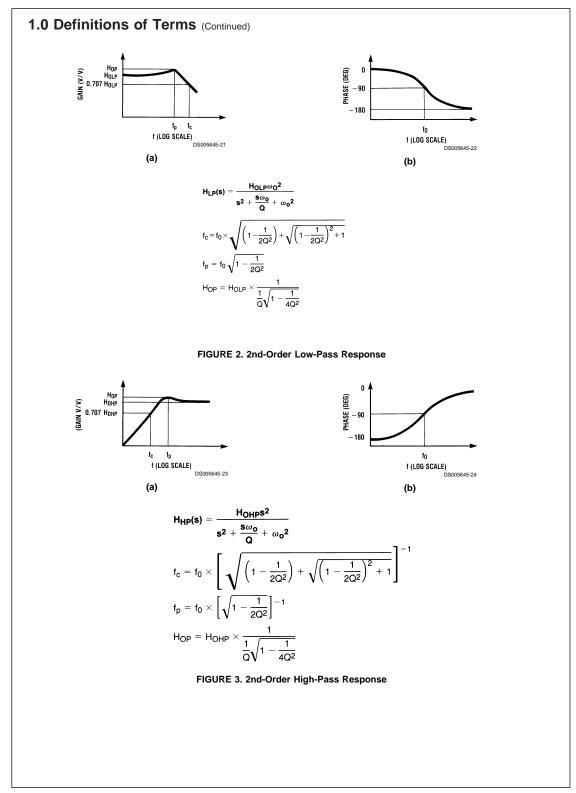

**H**<sub>OBP</sub>: the gain (in V/V) of the bandpass output at  $f = f_0$ .  $\textbf{H}_{\textbf{OLP}}\text{:}$  the gain (in V/V) of the lowpass output as  $f \rightarrow 0 \text{ Hz}$ (Figure 2).

$\textbf{H}_{\textbf{OHP}}$ : the gain (in V/V) of the highpass output as  $f \rightarrow f_{CLK}/2$ (Figure 3)

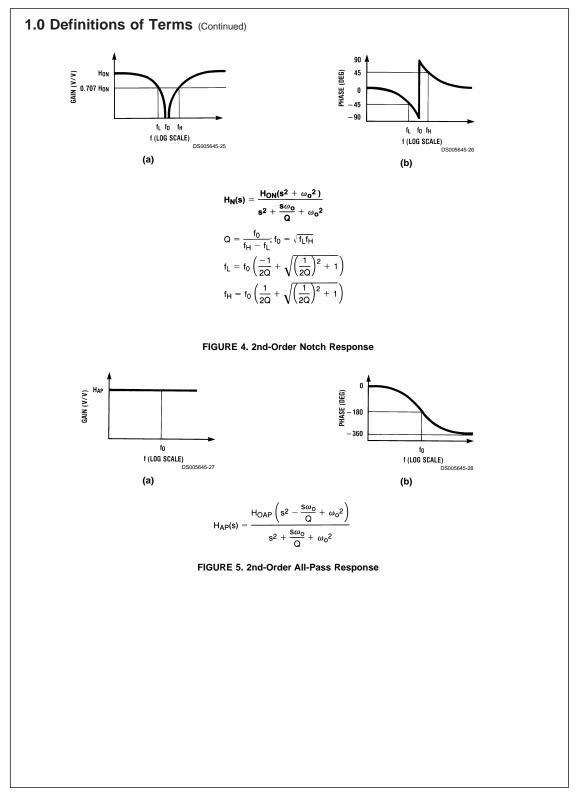

**H**<sub>ON</sub>: the gain (in V/V) of the notch output as  $f \rightarrow 0$  Hz and as  $f \rightarrow f_{\text{CLK}}/2,$  when the notch filter has equal gain above and below the center frequency (Figure 4). When the low-frequency gain differs from the high-frequency gain, as in modes 2 and 3a (Figure 10 and Figure 12), the two quantities below are used in place of  $\mathrm{H}_{\mathrm{ON}}.$

**H**<sub>ON1</sub>: the gain (in V/V) of the notch output as  $f \rightarrow 0$  Hz.  $\textbf{H}_{\textbf{ON2}}\text{:}$  the gain (in V/V) of the notch output as  $f \rightarrow f_{\text{CLK}}/2.$

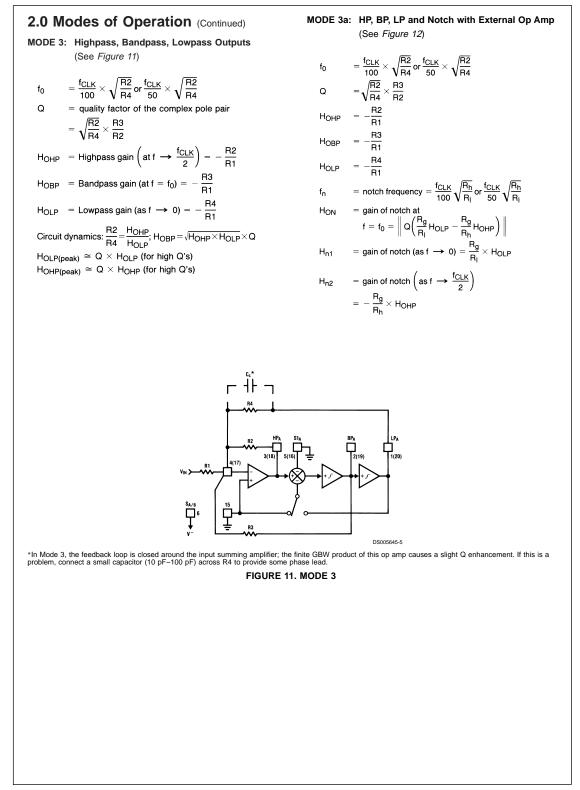

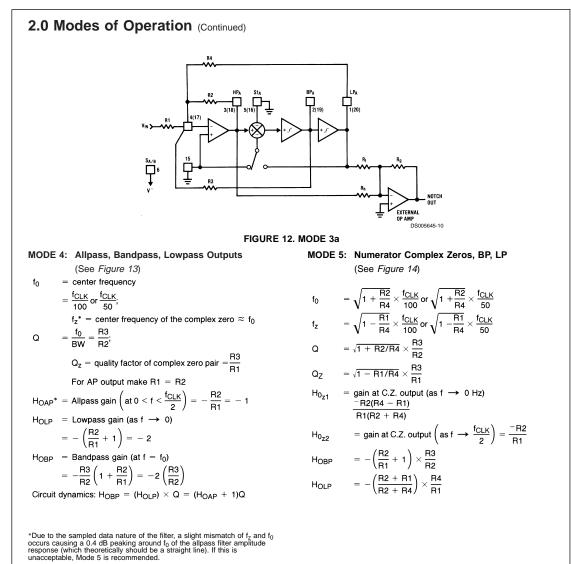

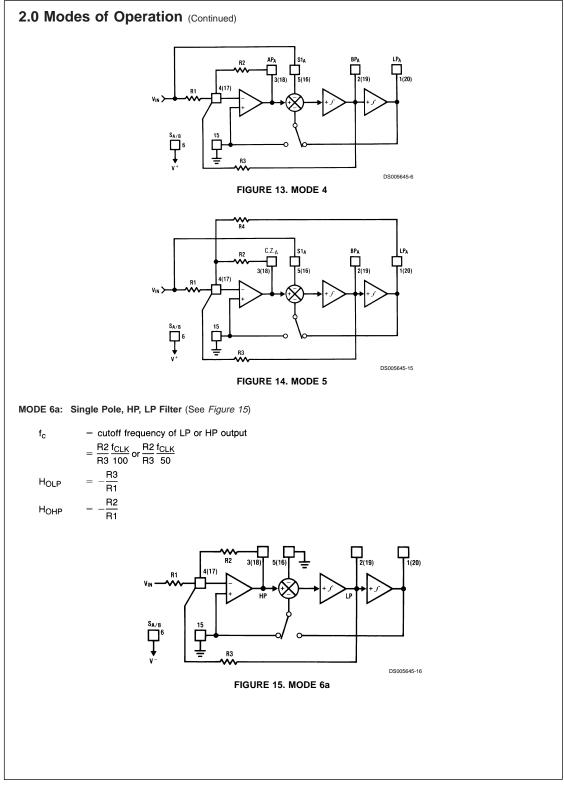

#### 2.0 Modes of Operation

The LMF100 is a switched capacitor (sampled data) filter. To fully describe its transfer functions, a time domain analysis is appropriate. Since this is cumbersome, and since the LMF100 closely approximates continuous filters, the following discussion is based on the well-known frequency domain. Each LMF100 can produce two full 2nd order functions. See *Table 1* for a summary of the characteristics of the various modes.

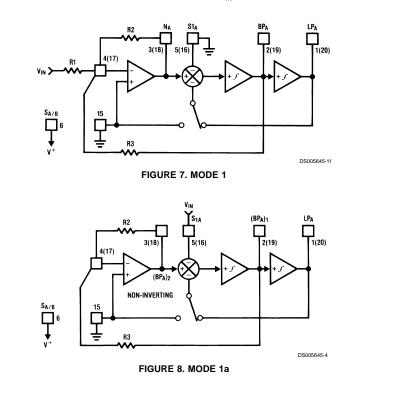

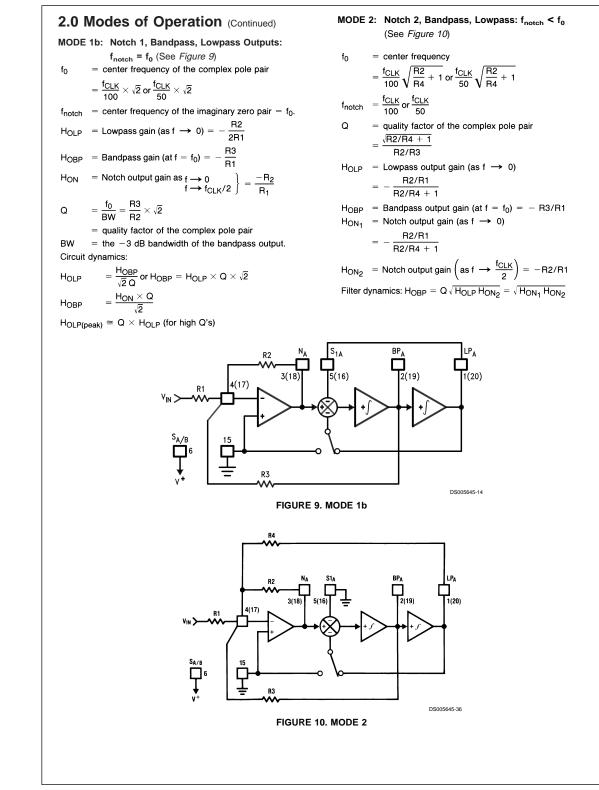

MODE 1: Notch 1, Bandpass, Lowpass Outputs:

$$f_{notch} = f_0$$

(See Figure 7)

$f_0$  = center frequency of the complex pole pair

$$=\frac{f_{CLK}}{100} \text{ or } \frac{f_{CLK}}{50}$$

$f_{notch}$  = center frequency of the imaginary zero pair =  $f_0$ .

$$H_{OLP}$$

= Lowpass gain (as f  $\rightarrow$  0) =  $-\frac{R2}{R1}$

$$H_{OBP}$$

= Bandpass gain (at f = f<sub>0</sub>) =  $-\frac{H_3}{R_1}$

$$H_{ON} = \text{Notch output gain as } \underset{f \to f_{CLK}/2}{\text{s}} = \frac{-R_2}{R_1}$$

$$Q \qquad = \frac{f_0}{BW} = \frac{R3}{R2}$$

= quality factor of the complex pole pair

$$BW = the -3 dB bandwidth of the bandpass output.$$

Circuit dynamics:

$$\begin{aligned} H_{OLP} &= \frac{H_{OBP}}{Q} \text{ or } H_{OBP} = H_{OLP} \times Q \\ &= H_{ON} \times Q. \end{aligned}$$

$H_{OLP(peak)} \cong Q \times H_{OLP}$  (for high Q's)

MODE 1a: Non-Inverting BP, LP (See Figure 8)

$$\begin{array}{ll} f_{0} & = \displaystyle \frac{f_{CLK}}{100} \, \text{or} \, \frac{f_{CLK}}{50} \\ Q & = \displaystyle \frac{R3}{R2} \\ H_{OLP} & = \displaystyle -1; \, H_{OLP(peak)} \cong Q \times H_{OLP} \, (\text{for high Q's}) \\ H_{OBP_{1}} & = \displaystyle -\frac{R3}{R2} \\ H_{ODD} & = \displaystyle 1 \, (\text{non-inverting}) \end{array}$$

Note:  $V_{IN}$  should be driven from a low impedance (<1 k $\Omega$ ) source.

Q

14