#### AGREGATION DE GENIE ELECTRIQUE SESSION 2004

#### **Option A: Electronique et informatique industrielle**

#### Epreuve d'électronique comportant un avant-projet

#### **AVERTISSEMENT**

#### L'épreuve se compose de 7 parties indépendantes repérées A, B, C, D, E, F et G

À l'intérieur de chaque partie les questions sont également indépendantes. Les candidats sont invités à prendre connaissance de la totalité du sujet avant de commencer à composer.

Le sujet comprend un jeu de documents réponse à compléter. Les candidats devront :

- Impérativement utiliser le document réponse à chaque fois que cela sera précisé dans la guestion ;

- Impérativement utiliser les notations indiquées dans le texte ou sur les figures ;

- Rédiger sur des feuilles séparées les réponses à chaque partie et numéroter chaque page de leur copie ;

- Présenter les calculs clairement, dégager et encadrer tout résultat littéral ou numérique ;

- Expliquer le raisonnement utilisé entre deux étapes de calcul.

#### **Note importante:**

Une partie du barème, lors de la correction, sera affectée :

- à la présentation générale de la copie ;

- à la concision des explications et à la précision du vocabulaire utilisé ;

- à la lisibilité et à la présentation des calculs mathématiques ;

- au respect de la numérotation des questions que l'on doit retrouver devant les réponses.

#### Conseil aux candidats:

Si le texte du sujet, de ses questions ou de ses annexes, vous conduit à formuler une ou plusieurs hypothèses, il vous est demandé de la (ou les) mentionner explicitement dans votre copie.

#### Ce sujet comporte :

- un dossier présentation;

- un dossier schémas constructeurs;

- un dossier documentations ressource;

- un dossier questionnement;

- 10 pages document réponse.

# SYSTEME DE PALPAGE A TRANSMISSION RADIO ETUDE DU RECEPTEUR (MI16)

## **DOSSIER DE PRESENTATION**

## Contenu du dossier :

| 1. PRESENTATION DU SYSTEME DE PALPAGE A TRANSMISSION RADI | [ <b>0</b> 1 |

|-----------------------------------------------------------|--------------|

| 1.1. DESCRIPTION DU FABRICANT.                            | 1            |

| 1.2. DIAGRAMME SAGITTAL.                                  | 2            |

| 2. ANALYSE FONCTIONNELLE DE OT1 MODULE EMETTEUR RADIO     | 3            |

| 2.1. SCHEMA FONCTIONNEL DE DEGRE 1                        | 3            |

| 2.2. SCHEMA FONCTIONNEL DE DEGRE 2 DE FP2                 | 4            |

| 2.3. SCHEMA FONCTIONNEL DE DEGRE 2 DE FP5.                | 5            |

| 3. ANALYSE FONCTIONNELLE DE OT4 MODULE RECEPTEUR RADIO    | 6            |

| 3.1. SCHEMA FONCTIONNEL DE DEGRE 1                        | 6            |

| 3.2 SCHEMA FONCTIONNEL DE DECRE 2 DE EPS                  | 8            |

# 1. PRESENTATION DU SYSTEME DE PALPAGE A TRANSMISSION RADIO.

#### 1.1. DESCRIPTION DU FABRICANT.

## **MP16**

Système de palpage à transmission radio pour centres d'usinage et tours de grandes dimensions

#### Description du système

Le MP16 comprend un palpeur Renishaw MP3 associé à un système de transmission des signaux par radio. L'intégration de l'ensemble de palpage est rapide et aisée puisqu'il n'y a plus de cablâge à réaliser.

Le montage en brôche du palpeur s'effectue grace à un cône sur lequel est fixé le module émetteur RMP2, le palpeur MP3 et son stylet.

Le système MP16 utilise un des 69 canaux alloués dans la bande UHF des 433 Mhz. L'utilisateur peut lui mème programmer les canaux ainsi que le mode de mise en marche désiré grace à un dialogue optique entre le palpeur et l'interface MI 16.

L'interface MI 16 intègre 2 récepteurs radio distincts, raccordés chacun à une antenne. Ce dispositif permet de minimiser les phénomènes d'échos lors des déplacements du MP16.

La mise en route du palpeur radio MP16 peut être effectuée selon plusieurs modes :

- Interrupteur dans le cône.

- M / A par rotation.

- Commande optique (code M)

Le sytème est opérationel jusque à une distance d'environ 15m entre l'émetteur RMP2 du palpeur MP 16 et les antennes RMM2.

#### Description des éléments

MP3 Palpeur à déclenchement  $\pm X$ ,  $\pm Y$ , +Z.

RMP2 Module émetteur radio.

RMM2 Antennes de réception signal radio.

MI16 Récepteur radio et interfaçage CN.

PSU3 Alimentation 24v (Optionnelle).

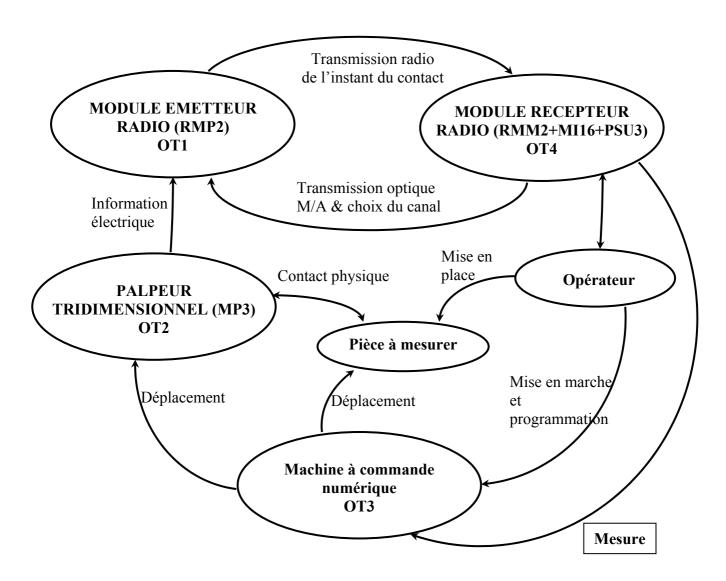

#### 1.2. DIAGRAMME SAGITTAL.

#### Fonction d'usage:

Le système technique doit pouvoir faire des mesures sur des pièces mécaniques (hauteur, largeur, diamètre, ...) avec une précision allant jusqu'au micromètre. Les mesures seront entièrement automatiques et reproductibles.

# 2. ANALYSE FONCTIONNELLE DE OT1 MODULE EMETTEUR RADIO.

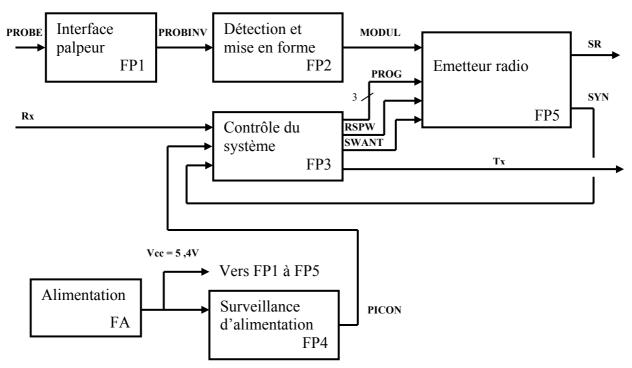

#### 2.1. SCHEMA FONCTIONNEL DE DEGRE 1.

#### **Description des fonctions:**

#### ◆ FP1 : Interface palpeur.

Cette fonction permet de remettre en forme le signal issu du contact du palpeur.

- ➤ **Entrée** : PROBE, signal binaire (0 ;5,4V) représentant l'état du palpeur (0V correspondant au palpeur en contact avec la pièce).

- > **Sortie**: PROBINV, signal binaire (0;5,4V) inversé par rapport à PROBE (5,4V correspondant au palpeur en contact avec la pièce).

#### • FP2 : Détection et mise en forme.

Cette fonction permet de fournir l'instant précis où le palpeur est entré en contact.

- > **Entrée** : PROBINV, issu de FP1.

- ➤ **Sortie**: MODUL, signal analogique (0;5V) comportant trois composantes fréquentielles. Un premier signal à 1kHz et modulé en phase (PSK) contenant à la fois une information de palpeur en contact, mais aussi l'instant précis où a eu lieu le contact. Cette information est transmise en série. Un second signal à 500Hz permet de récupérer l'horloge d'émission à 1kHz. Pour finir un signal à 100Hz indique le bon état des piles.

#### ◆ FP3 : Contrôle du système.

Cette fonction permet de dialoguer par liaison série optique avec OT4 pour obtenir l'ordre de mise en marche et d'arrêt ainsi que le numéro de canal de transmission choisi. Elle contrôle le bon fonctionnement du système.

#### > Entrées :

- ✓ Rx, signal optique de réception série.

- ✓ PICON, signal logique issu de FP4 indiquant le bon état des piles.

- ✓ SYN, signal logique issu de FP5 indiquant le bon fonctionnement de l'émetteur.

#### > Sorties :

- ✓ RSPW, signal logique commandant l'alimentation de l'émetteur (1 logique pour mise en marche).

- ✓ SWANT signal logique commandant la connexion de l'antenne à la sortie de l'émetteur.

✓ PROG, liaison série synchrone comportant trois fils (ENABLE, DATA et CLOCK) pour l'initialisation de l'émetteur (entre autre la fréquence d'émission).

#### **♦** FP4 : Surveillance d'alimentation.

Cette fonction permet de détecter l'usure des piles d'alimentation de l'émetteur radio.

- > Entrée : tension des piles (5,4V).

- > **Sortie** : PICON, signal binaire indiquant un bon état des piles.

#### FP5 : Emetteur radio.

Cette fonction permet de transmettre par liaison radio l'information issue de FP2.

#### > Entrées :

- ✓ MODUL, signal analogique issu de FP2 représentant principalement la mesure faite.

- ✓ RSPW, signal logique commandant l'alimentation de l'émetteur (1 logique pour mise en marche).

- ✓ SWANT signal logique commandant la connexion de l'antenne à la sortie de l'émetteur.

- ✓ PROG, liaison série synchrone comportant trois fils (ENABLE, DATA et CLOCK) pour l'initialisation de l'émetteur (entre autre la fréquence d'émission).

#### > Sorties :

- ✓ SR, signal radio à 433MHz sur un des 69 canaux.

- ✓ SYN, signal logique indiquant le bon fonctionnement de l'émetteur.

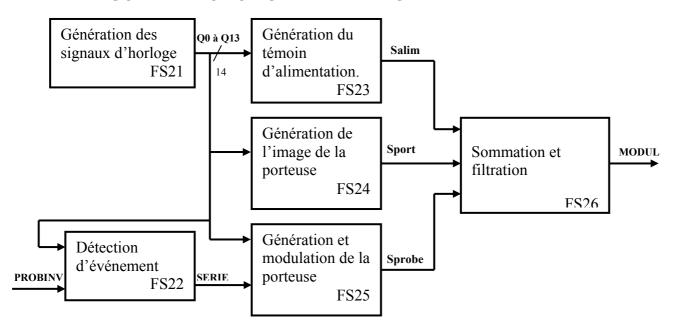

#### 2.2. SCHEMA FONCTIONNEL DE DEGRE 2 DE FP2.

#### **Description des fonctions:**

#### FS21 : Génération des signaux d'horloge.

Cette fonction permet de générer tous les signaux d'horloge utile au fonctionnement de FP2. Les différentes horloges sont issues d'un quartz à 4MHz.

➤ **Sorties**: Q0 à Q13, signaux binaires de rapport cyclique ½, de fréquence moitié l'un par rapport à l'autre. Q0 à 1MHz, Q1 à 500kHz, ..., Q13 à 122Hz.

#### • FS22 : Détection d'événement.

Cette fonction permet de détecter le moment précis où le palpeur est entré en contact.

#### > Entrées :

- ✓ Q0 à Q13, signaux d'horloge.

- ✓ PROBINV, issu de FP1.

- ➤ **Sortie**: SERIE, signal binaire représentant une émission en série au rythme du 976Hz (~1kHz). Sont envoyés les 8 bits (Q3 à Q10) capturés à l'événement sur PROBINV, poids faible en tête, ainsi qu'un bit de parité et enfin un bit représentant l'état du palpeur (lorsque le palpeur est en appui ce bit est à 1). En fin de transmission le signal SERIE garde l'état du dernier bit reçu (c'est à dire : état du palpeur).

#### • FS23 : Génération du témoin d'alimentation.

Cette fonction permet de générer un signal sinusoïdal de fréquence 122Hz témoin du bon état des piles.

- > **Entrée** : Q0 à Q13, signaux d'horloge.

- > Sortie: Salim, signal guasi sinus de fréquence 122Hz et d'amplitude 0 à 5V.

#### FS24 : Génération de l'image de la porteuse.

Cette fonction permet de générer un signal sinusoïdal de fréquence 488Hz image (divisée par 2) de l'horloge d'émission du signal SERIE.

- > **Entrée** : Q0 à Q13, signaux d'horloge.

- > **Sortie** : Sport, signal quasi sinus de fréquence 488Hz et d'amplitude 0 à 5V.

#### • FS25 : Génération et modulation de la porteuse.

Cette fonction permet de faire une modulation à saut de phase (PSK) pour transmettre le signal série issu de FS22.

#### > Entrées :

- ✓ Q0 à Q13, signaux d'horloge.

- ✓ SERIE, issu de FS22.

- > **Sortie** : Sprobe, signal quasi sinus de fréquence 976Hz, d'amplitude 0 à 5V et modulé en phase (en phase ou en opposition de phase).

#### • FS26 : Sommation et filtration.

Cette fonction permet de faire la somme pondérée des trois signaux à transmettre ainsi que le filtrage des harmoniques.

#### > Entrées :

- ✓ Salim, issu de FS23.

- ✓ Sport, issu de FS24.

- ✓ Sprobe, issu de FS25.

- > **Sortie**: MODUL, signal analogique d'amplitude 0 à 5V avec des composantes fréquentielles à 122Hz, 488Hz et le signal utile autour de 976Hz.

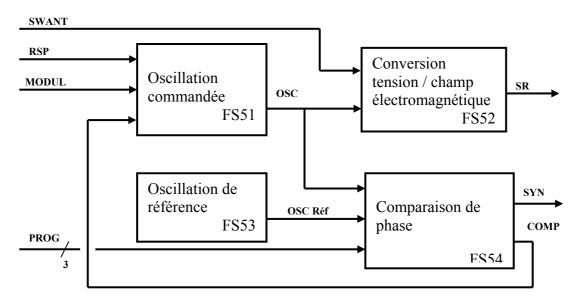

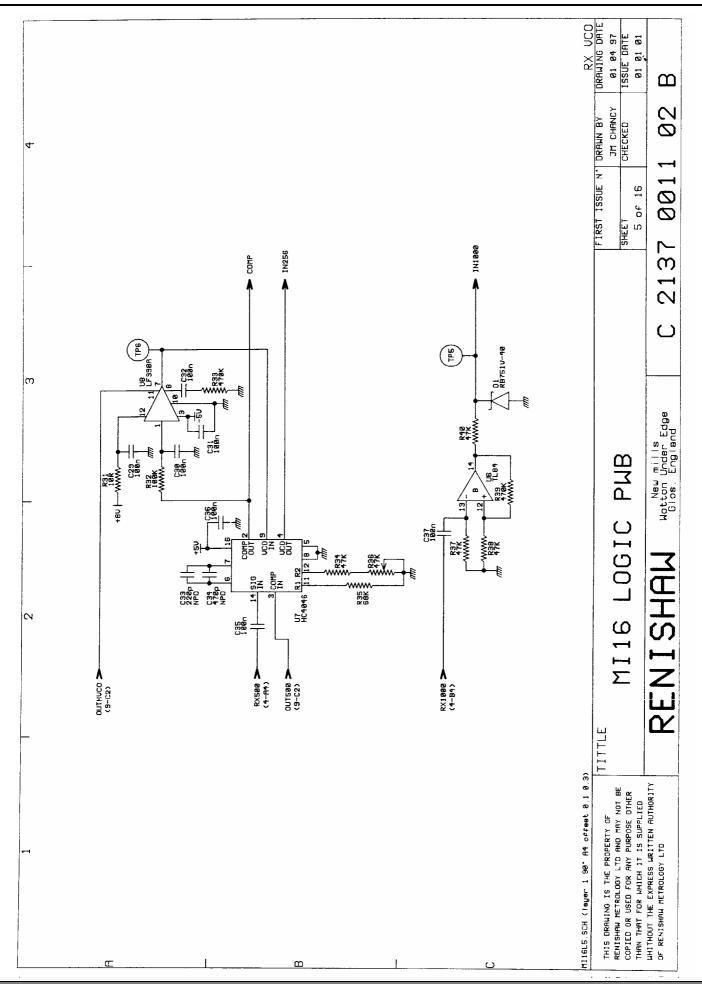

#### 2.3. SCHEMA FONCTIONNEL DE DEGRE 2 DE FP5.

#### **Description des fonctions:**

#### • FS51 : Oscillation commandée.

Cette fonction permet de réaliser un oscillateur commandé en tension.

#### > Entrées :

- ✓ RSPW, signal de mise en marche issu de FP3.

- ✓ MODUL, signal à transmettre issu de FP2.

- ✓ COMP, signal représentant l'erreur de phase issu de FS54.

- > **Sortie** : OSC, signal analogique sinusoïdal modulé en fréquence avec une porteuse dans la bande des 433MHz (69 canaux possibles).

#### ◆ FS52 : Conversion tension / champ électromagnétique.

Cette fonction permet de transformer le signal électrique en champ électromagnétique.

#### > Entrées :

- ✓ SWANT, ordre de connexion de l'antenne issu de FP3.

- ✓ OSC, issu de FS51.

- ➤ **Sortie**: SR, signal radio (champ électromagnétique) modulé en fréquence autour d'une porteuse à 433MHz. En fait 69 canaux sont possibles allant de 433,075MHz à 434,8MHz par pas de 25kHz.

#### FS53 : Oscillation de référence.

Cette fonction permet de générer une fréquence de référence pour faire le réglage de la fréquence d'émission.

> **Sortie** : OSC Réf, signal sinusoïdal de fréquence 8MHz et d'amplitude comprise entre 0 à 5V.

#### • FS54 : Comparaison de phase.

Cette fonction permet de fournir une tension image de l'erreur de phase entre deux signaux périodiques.

#### > Entrées :

- ✓ OSC, issu de FS51.

- ✓ OSC Réf, issu de FS53.

- ✓ PROG, signal de programmation issu de FP3.

#### > Sortie:

- ✓ SYN, signal logique indiquant la synchronisation des signaux d'entrée.

- ✓ COMP, tension analogique comprise entre 0 et 5V image de l'erreur de phase entre un signal de fréquence N1 fois plus faible que OSC et un signal de fréquence N2 fois plus faible que OSC Réf. Cette erreur est aussi filtrée dans la fonction. On peut avoir avant filtrage, une erreur de phase comprise entre 0 et 360°.

# 3. ANALYSE FONCTIONNELLE DE OT4 MODULE RECEPTEUR RADIO.

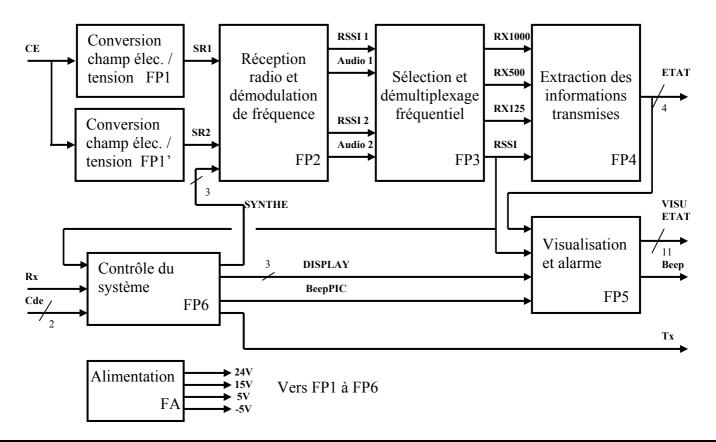

#### 3.1. SCHEMA FONCTIONNEL DE DEGRE 1.

#### **Description des fonctions:**

#### ◆ FP1, FP1': Conversion champ électromagnétique / tension.

Cette fonction permet de convertir l'onde électrique reçue en une tension.

- > **Entrée** : CE, champ électromagnétique autour de 433MHz provenant de l'émetteur.

- > **Sortie**: SR1, SR2, tensions analogiques de faible amplitude image de CE. La conversion se fait suivant deux axes perpendiculaires entre eux, l'une donne SR1, l'autre SR2.

#### • FP2 : Réception radio et démodulation de fréquence.

Cette fonction permet de démoduler (en fréquence) les signaux d'entrée sur le canal choisi.

#### > Entrées :

- ✓ SR1, SR2, issus de FP1 et FP1'.

- ✓ SYNTHE, liaison série synchrone (signal logique sur 3 bits, ENABLE, DATA et CLOCK) issu de FP6 servant à programmer le canal choisi.

#### > Sorties :

- ✓ Audio1, signal SR1 démodulé en fréquence sur le canal choisi et dans l'axe de la voie

1.

- ✓ RSSI1, signal analogique image du niveau de réception sur la voie 1.

- ✓ Audio2, RSSI2, même chose que Audio1 et RSSI1, mais pour SR2.

#### • FP3 : Sélection et démultiplexage fréquentiel.

Cette fonction permet de choisir le signal ayant la plus forte réception (Audio1 ou Audio2), puis de séparer les trois informations reçues.

> Entrées: RSSI1, Audio1,RSSI2, Audio2 signaux analogiques issus de FP2.

#### > Sorties :

- ✓ RX1000, signal analogique sinusoïdal de fréquence 976Hz, modulé en phase (PSK), contenant l'information sur l'état du palpeur ainsi que le moment (dans une période du 976Hz) où le palpeur a changé d'état (mot de 8 bits utiles).

- ✓ RX500, signal analogique sinusoïdal de fréquence 488Hz image de la fréquence d'émission (divisée par 2) du signal PSK.

- ✓ RX125, signal analogique sinusoïdal de fréquence 122Hz, témoin du bon état des piles de l'émetteur.

- ✓ RSSI, signal analogique image du niveau de réception.

#### • FP4 : Extraction des informations transmises.

Cette fonction permet de fournir les informations logiques transmises par l'émetteur. Principalement, le moment exact où le palpeur a changé d'état (après démodulation PSK et conversion nombre => temps).

- ➤ Entrée : Tensions RX1000, RX500, RX125, RSSI, issues de FP3.

- > **Sortie**: ETAT, signal binaire sur 4 bits indiquant l'état du palpeur et transmis vers la machine à commande numérique.

- ✓ PROBE STATUS, représentant l'état du palpeur (en contact ou non).

- ✓ ERROR, indiquant une erreur de transmission.

- ✓ LOW BATTERY, indiquant l'état des piles de l'émetteur.

- ✓ LOW SIGNAL, indiquant un niveau de réception trop faible pour le bon fonctionnement du système.

#### **♦** FP5 : Visualisation et alarme.

Cette fonction permet de réaliser l'interface avec l'opérateur, à la fois de façon visuelle pour fournir l'état du palpeur et le niveau de réception, mais aussi sonore pour avertir d'un problème et pour confirmer les commandes de l'opérateur (mise en marche et choix du canal de transmission).

#### > Entrées :

- ✓ ETAT, signal binaire sur 4 bits issu de FP4, indiquant l'état du palpeur.

- ✓ RSSI, signal analogique issu de FP3, indiquant le niveau de réception.

- ✓ DISPLAY, liaison série synchrone comportant trois fils (ENABLE, DATA et CLOCK) issue de FP6 pour transmettre les valeurs à afficher concernant la programmation du numéro de canal.

- ✓ BeepPIC, signal logique issu de FP6 demandant une impulsion sonore sur le haut parleur.

#### > Sorties :

✓ VISU ETAT, représente un ensemble de signaux visuels composé de :

- 1 bargraph indiquant le niveau de réception de la transmission radio.

- 2 afficheurs 7 segments indiquant le numéro de canal de transmission.

- 5 diodes électro-luminescentes (DEL) d'indications pour aider l'opérateur à programmer le numéro de canal sur le récepteur et sur l'émetteur (TIMEOUT, SHANK, SPIN, OPTIC et ON/OFF).

- 4 DELs indiquant si le palpeur est en contact, s'il y a une erreur de transmission, si la batterie de l'émetteur est déchargée et si le signal radio est trop faible.

- ✓ Beep, signal sonore d'avertissement de l'opérateur.

#### FP6 : Contrôle du système.

Cette fonction permet de dialoguer, par liaison série optique, avec OT1 pour lui envoyer l'ordre de M/A ainsi que le numéro de canal de transmission choisi.

Elle va également permettre le réglage exact de la fréquence de réception (FP2) et gérer les commandes d'affichage (Fp5).

#### > Entrées :

- ✓ RX, signal optique de réception série.

- ✓ RSSI, signal analogique issu de FP3, indiquant le niveau de réception.

- ✓ Deux signaux de commande permettant la mise en M/A et le choix du canal de réception.

#### > Sorties :

- ✓ SYNTHE, liaison série synchrone (signal logique sur 3 bits, ENABLE, DATA et CLOCK) servant à programmer le canal choisi.

- ✓ DISPLAY, liaison série synchrone comportant trois fils (ENABLE, DATA et CLOCK) pour transmettre les valeurs à afficher concernant la programmation du numéro de canal.

- ✓ BeepPIC, signal logique demandant une impulsion sonore sur le haut parleur.

- TX, signal optique de transmission série.

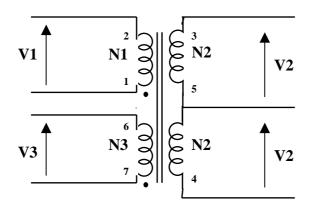

#### FA: Alimentation.

Cette fonction permet de fournir toutes les tensions nécessaires au bon fonctionnement du récepteur.

- > Entrée : Réseau 230V alternatif (EDF).

- > **Sorties**: Tensions continues de:

- ✓ +24V, 50mA.

- ✓ +15V, 100mA.

- ✓ +5V, 100mA.

- ✓ -5V, 100mA.

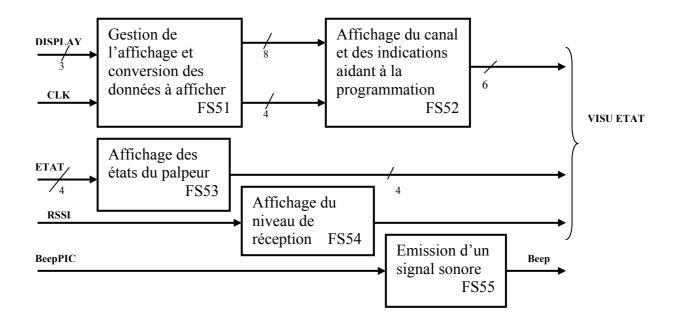

#### 3.2. SCHEMA FONCTIONNEL DE DEGRE 2 DE FP5.

#### **Description des fonctions:**

#### • FS51 : Gestion de l'affichage et conversion des données à afficher.

Cette fonction permet de commander le bon afficheur au bon moment avec les données correspondantes. Elle réalise également une conversion des données pour obtenir une donnée au format afficheur 7 segments.

#### > Entrées :

- ✓ DISPLAY, liaison série synchrone comportant trois fils (ENABLE, DATA et CLOCK) issue de FP6 pour transmettre les valeurs à afficher concernant la programmation du numéro de canal.

- ✓ CLK, signal d'horloge.

#### > Sorties :

- √ 8 signaux représentatifs des données à afficher au format 7 segments.

- √ 4 signaux de commande de choix de l'afficheur.

#### ◆ FS52 : Affichage du canal et des indications aidant à la programmation.

Cette fonction permet d'afficher le canal choisi ainsi que des indications nécessaires à l'opérateur pour la programmation.

#### > Entrées :

- 8 signaux représentatifs des données à afficher au format 7 segments.

- ✓ 4 signaux de commande de choix du bon afficheur.

#### > Sortie:

- ✓ Signaux affichés:

- 2 afficheurs 7 segments indiquant le numéro de canal de transmission.

- 5 diodes électro-luminescentes (DEL) d'indications pour aider l'opérateur à programmer le numéro de canal sur le récepteur et sur l'émetteur (TIMEOUT, SHANK, SPIN, OPTIC et ON/OFF).

#### FS53 : Affichage des états du palpeur.

Cette fonction permet l'affichage des différents états du palpeur

- > Entrées : : ETAT, signal binaire sur 4 bits indiquant l'état du palpeur

- ✓ PROBE STATUS, représentant l'état du palpeur (en contact ou non).

- ✓ ERROR, indiquant une erreur de transmission.

- ✓ LOW BATTERY, indiquant l'état des piles de l'émetteur.

- ✓ LOW SIGNAL, indiquant un niveau de réception trop faible pour le bon fonctionnement du système.

#### > Sortie:

- ✓ Signaux affichés :

- 4 DELs indiquant si le palpeur est en contact, s'il y a une erreur de transmission, si la batterie de l'émetteur est déchargée et si le signal radio est trop faible.

#### ◆ FS54 : Affichage du niveau de réception.

Cette fonction permet l'affichage du niveau de réception.

- > Entrée : RSSI, signal analogique issu de FP3, indiquant le niveau de réception.

- Sortie

- √ 1 bargraph indiquant le niveau de réception de la transmission radio.

#### • FS55 : Emission d'un signal sonore.

Cette fonction permet de produire un signal sonore pour avertir d'un problème.

#### > Entrée :

✓ BeepPIC, signal logique demandant une impulsion sonore sur le haut parleur.

#### > Sortie:

✓ Beep, signal sonore d'avertissement de l'opérateur.

# SYSTEME DE PALPAGE A TRANSMISSION RADIO ETUDE DU RECEPTEUR (MI16)

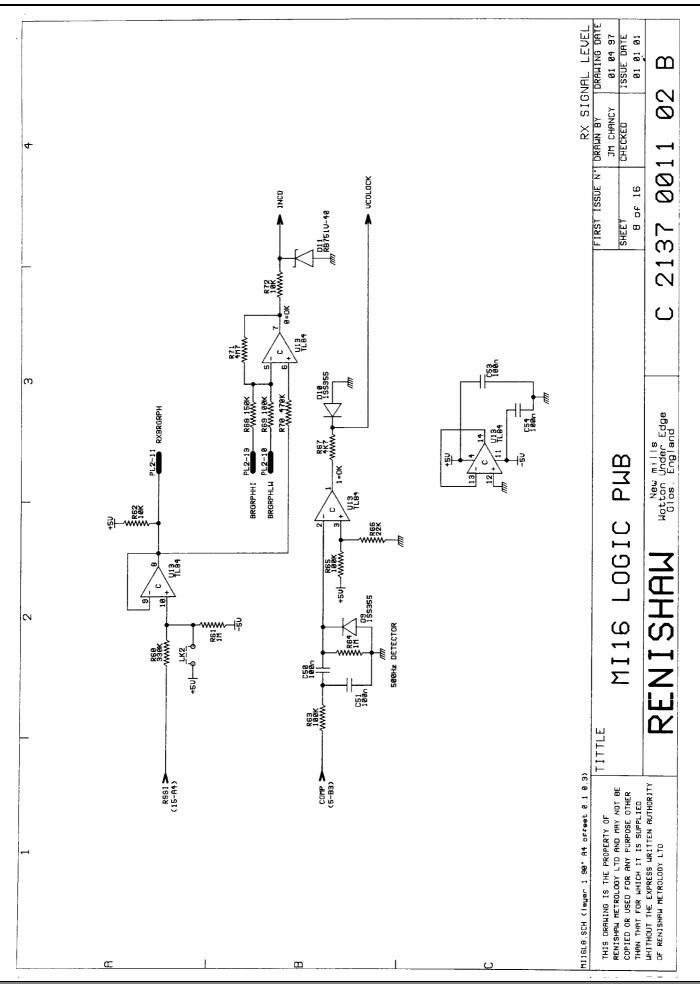

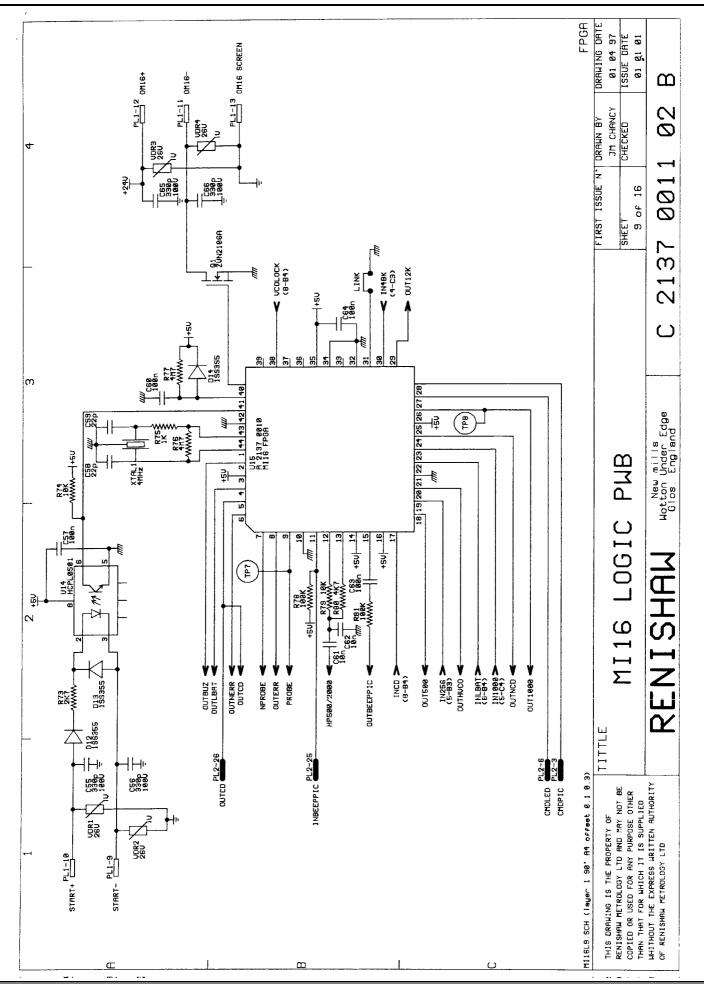

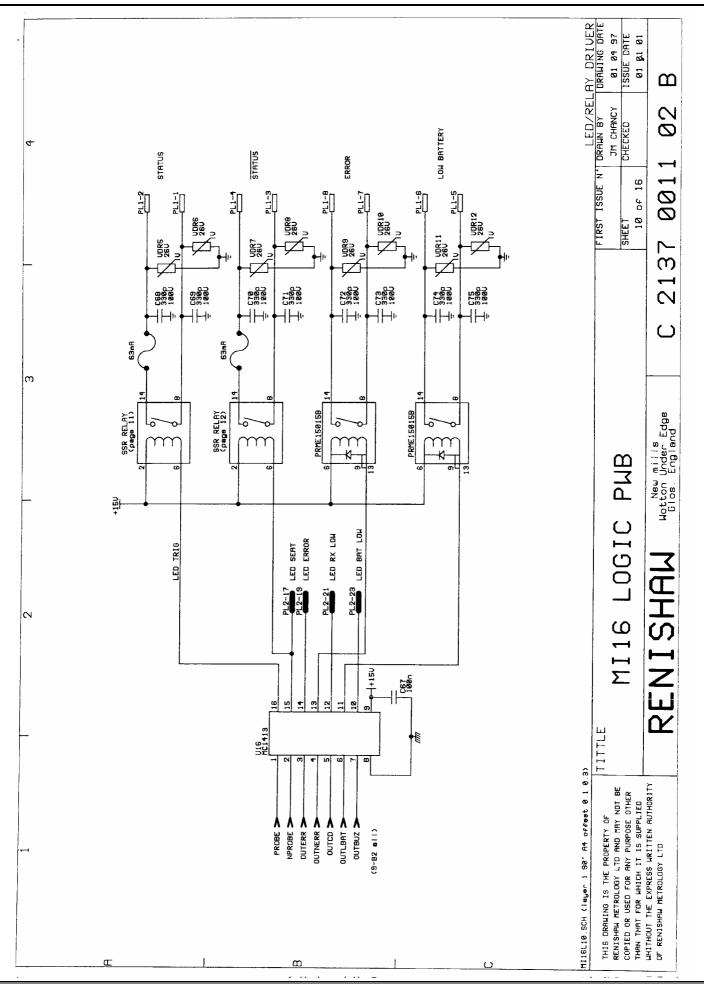

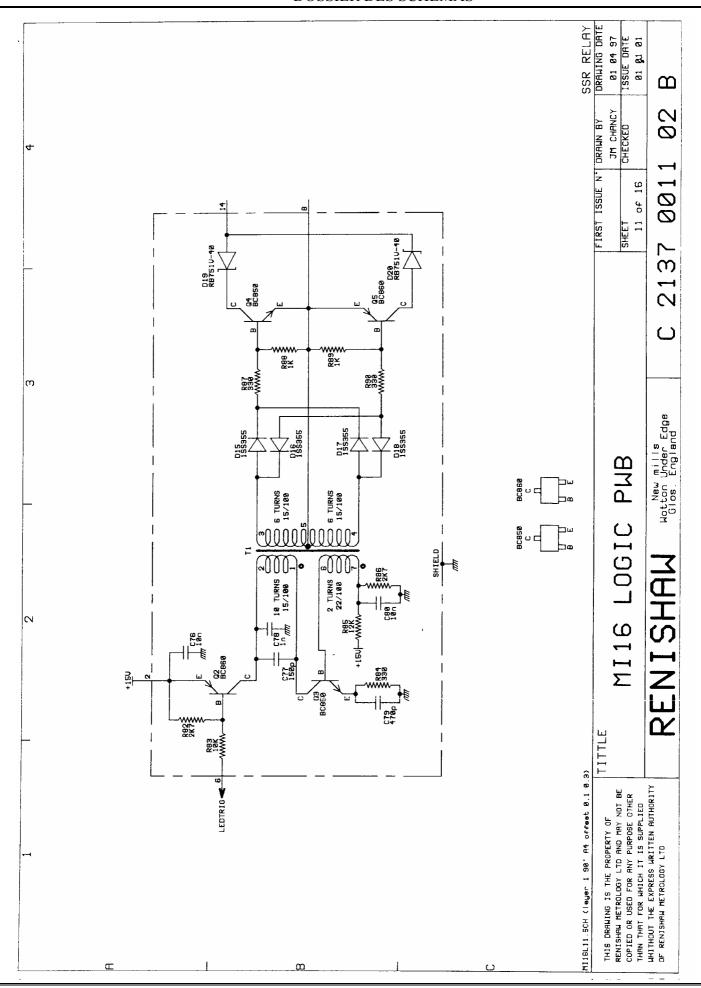

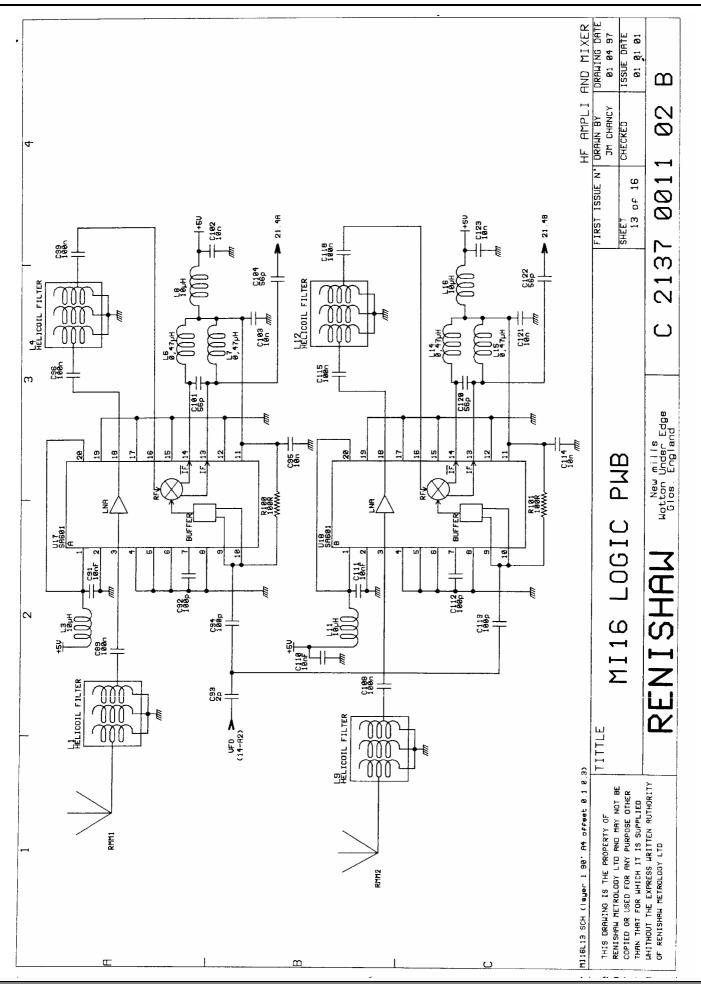

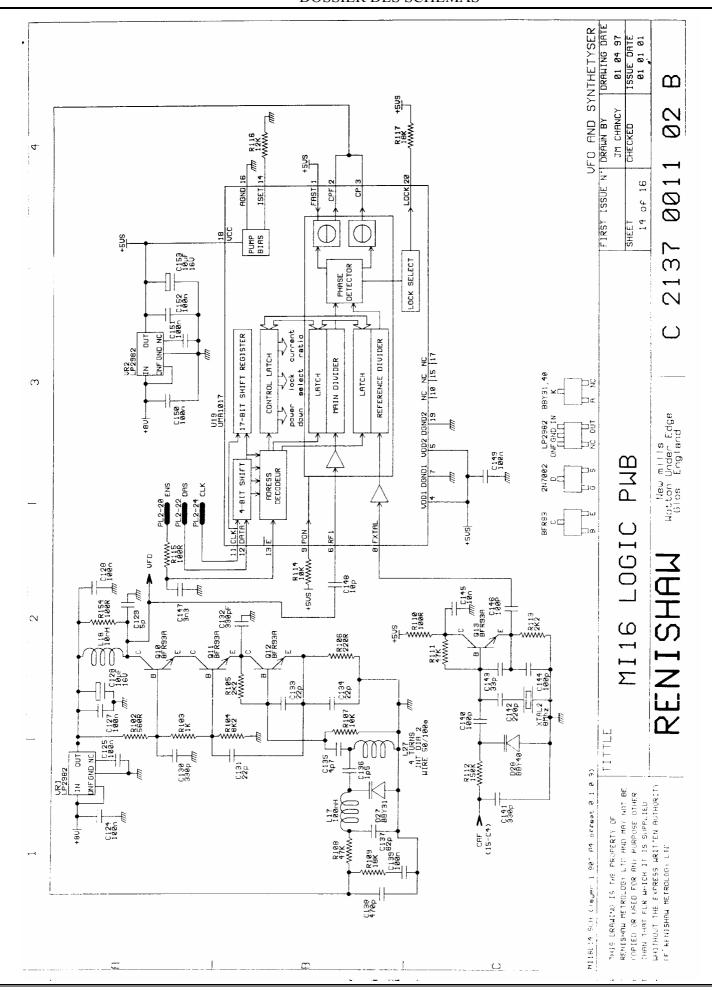

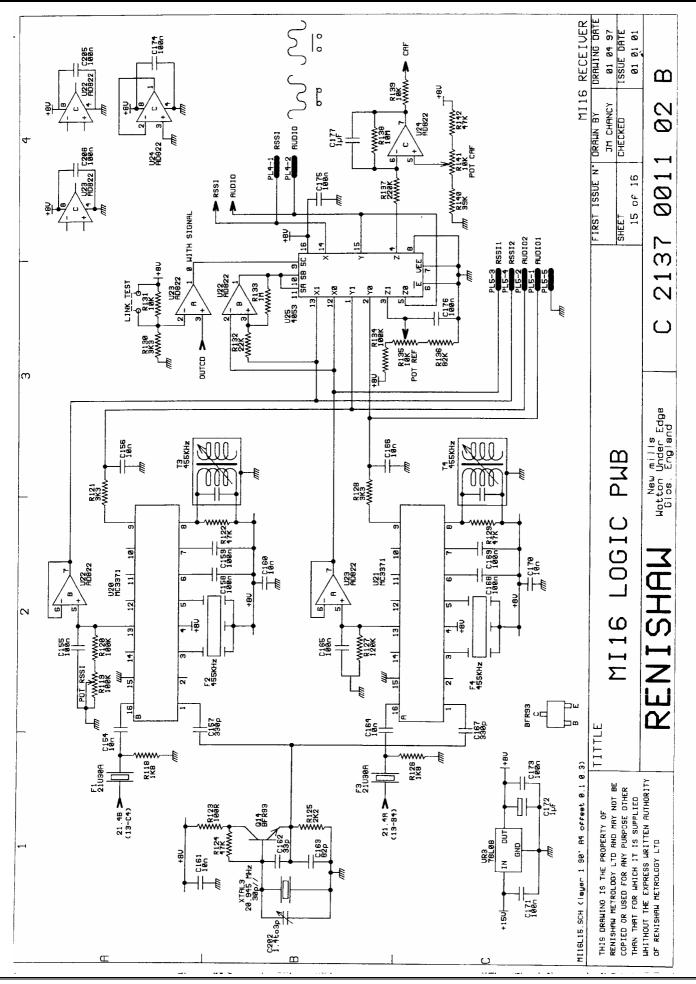

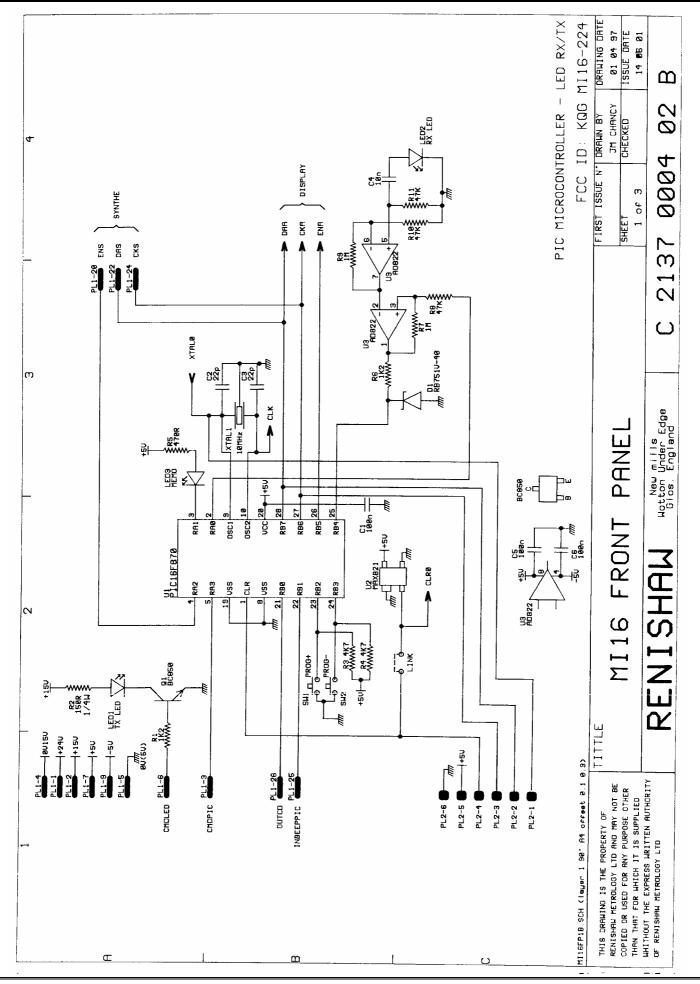

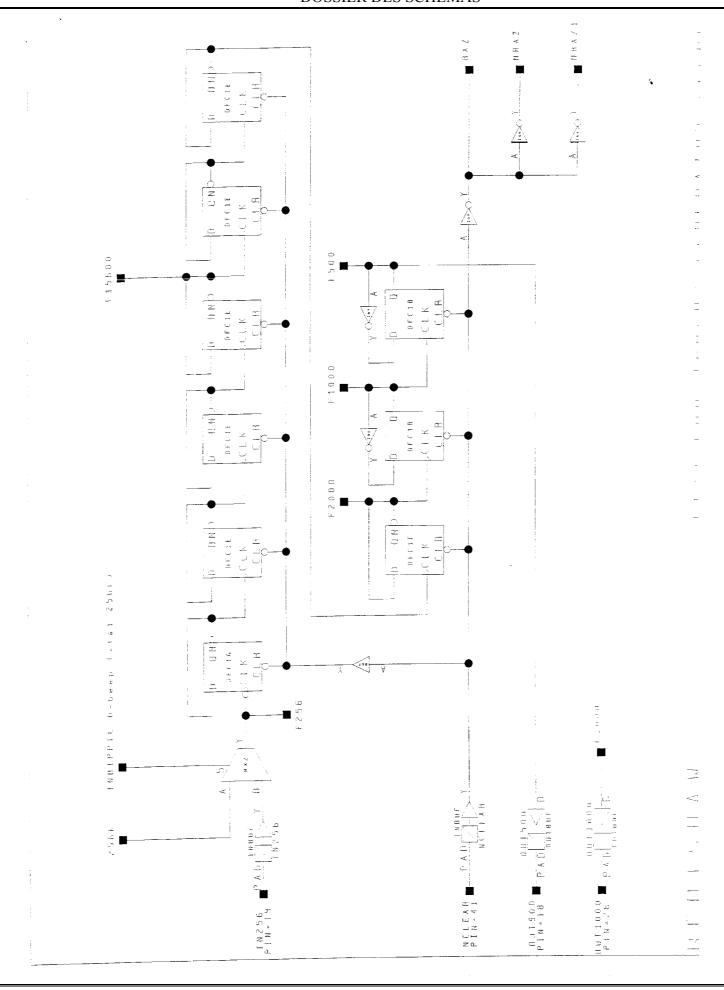

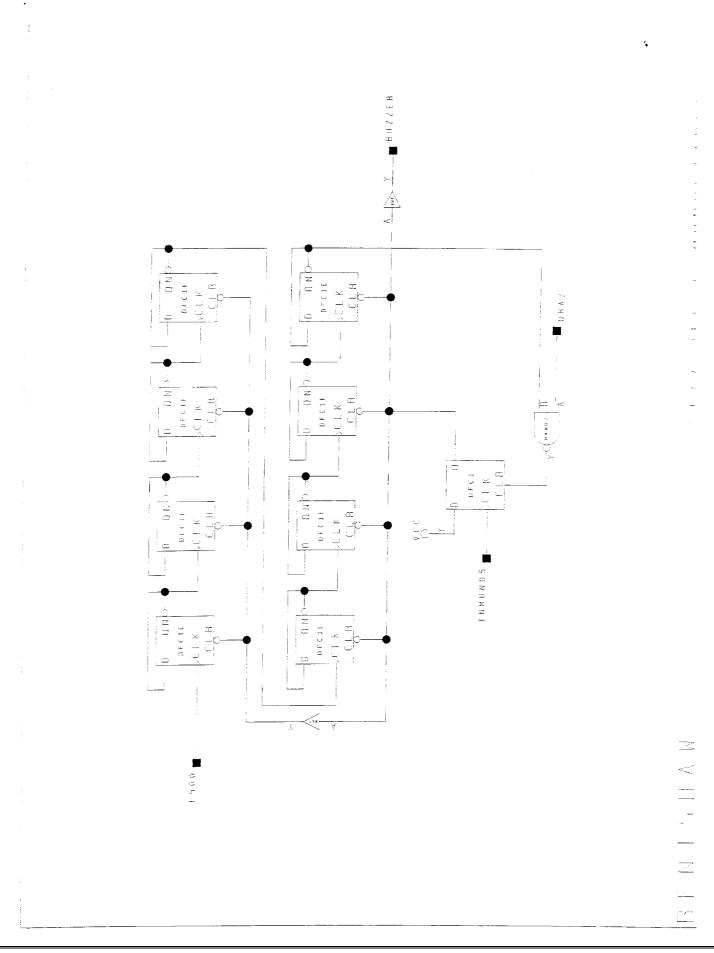

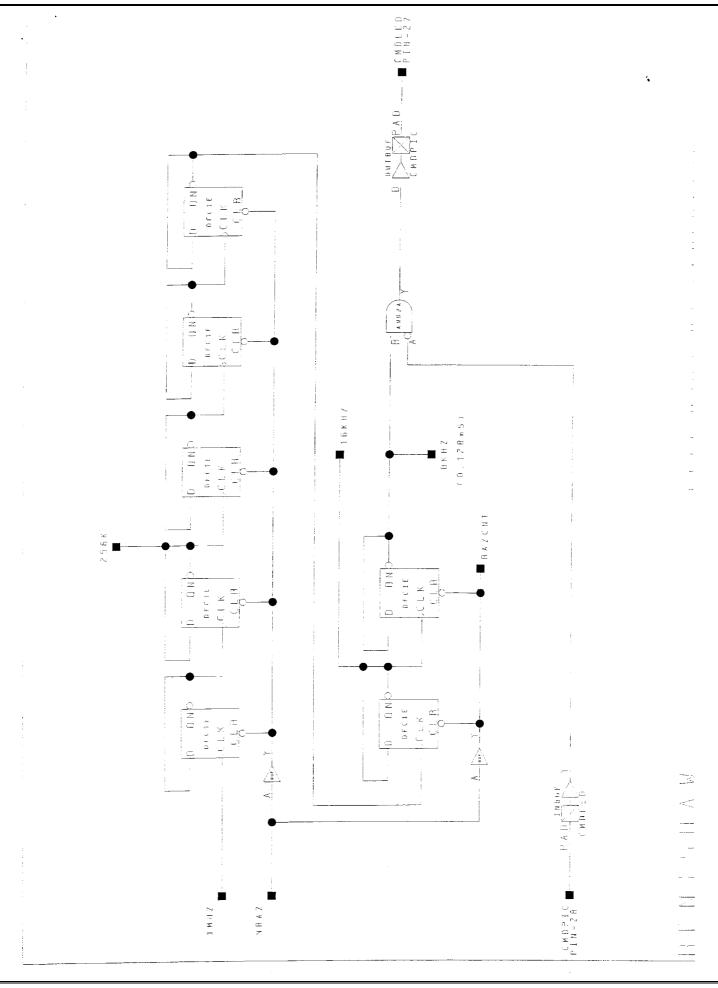

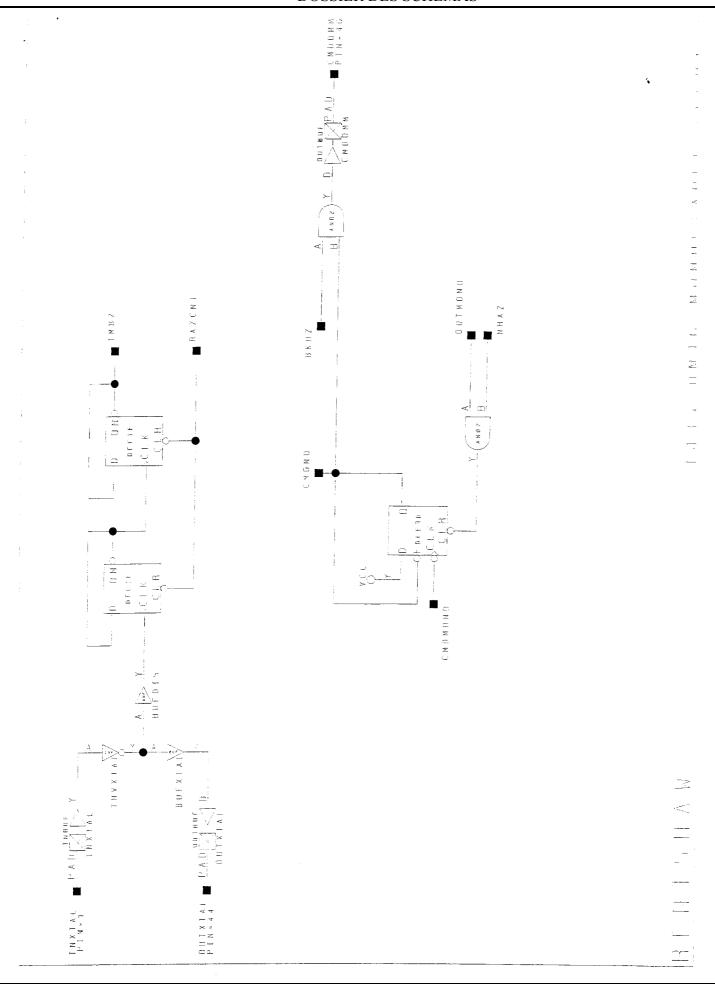

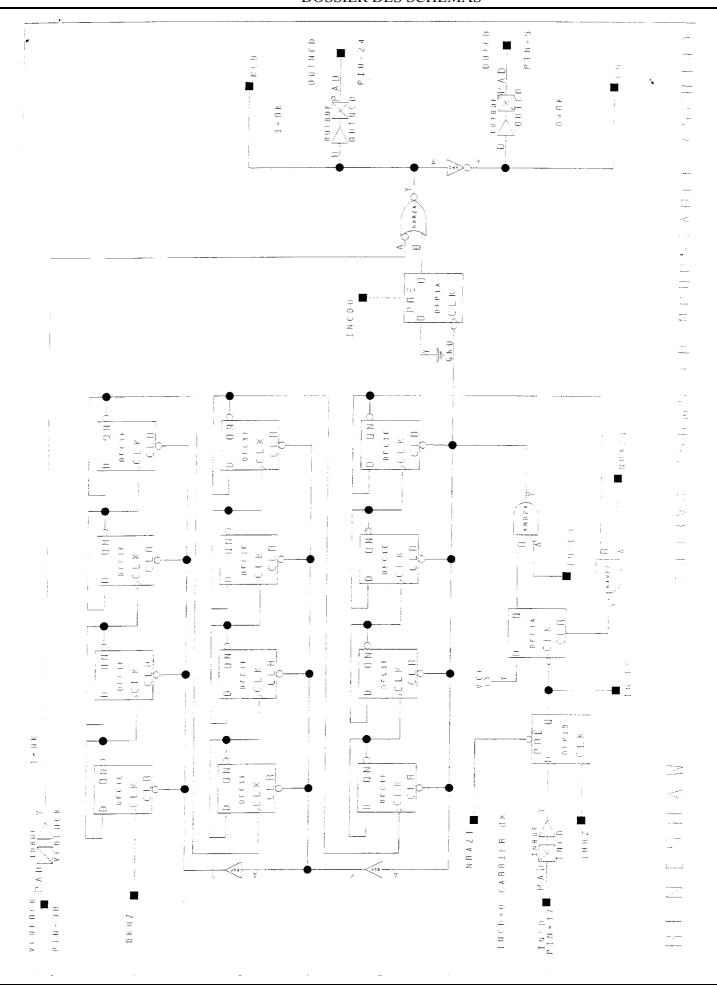

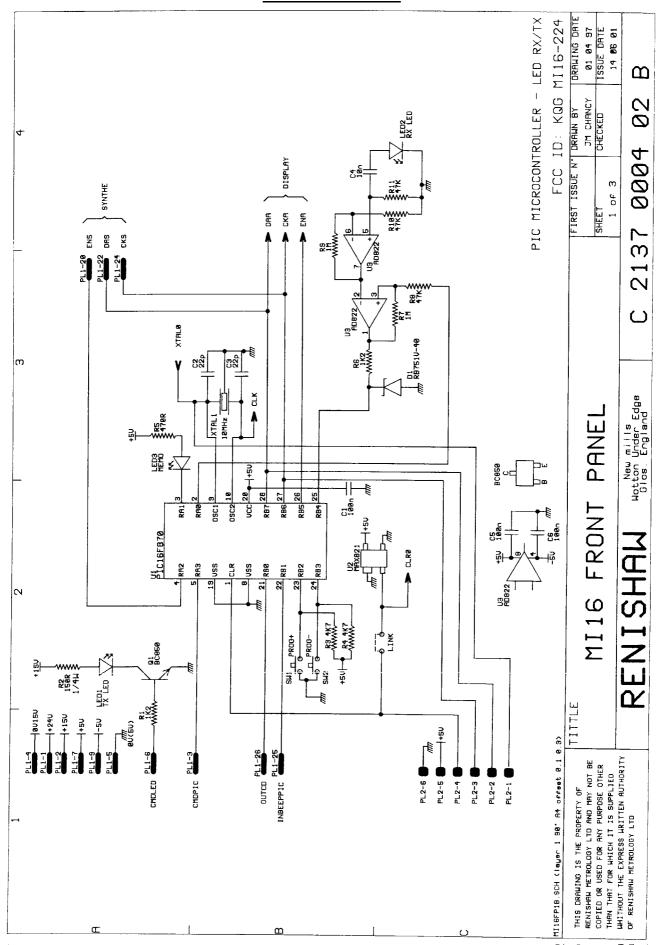

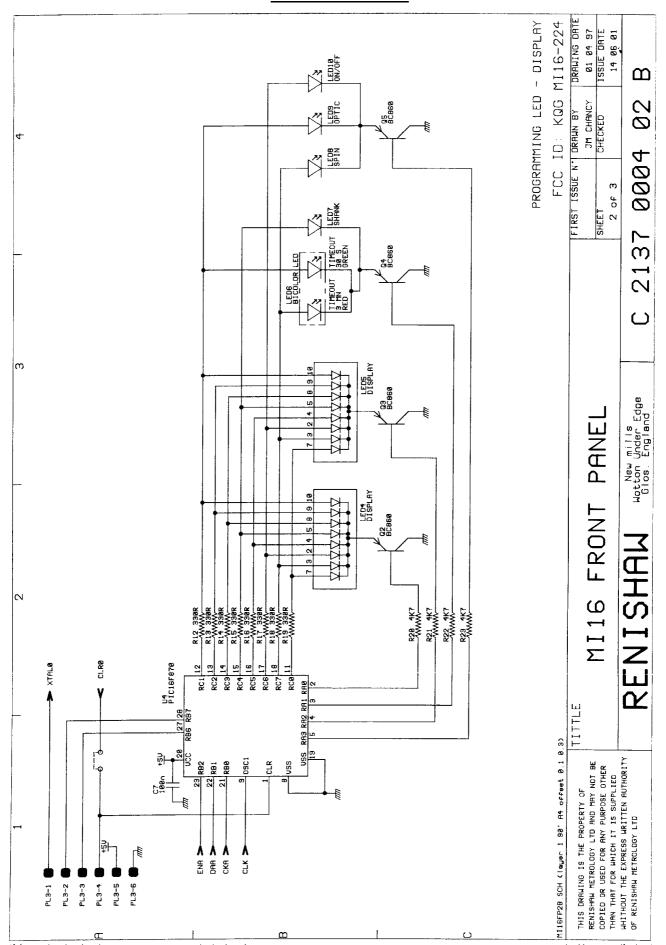

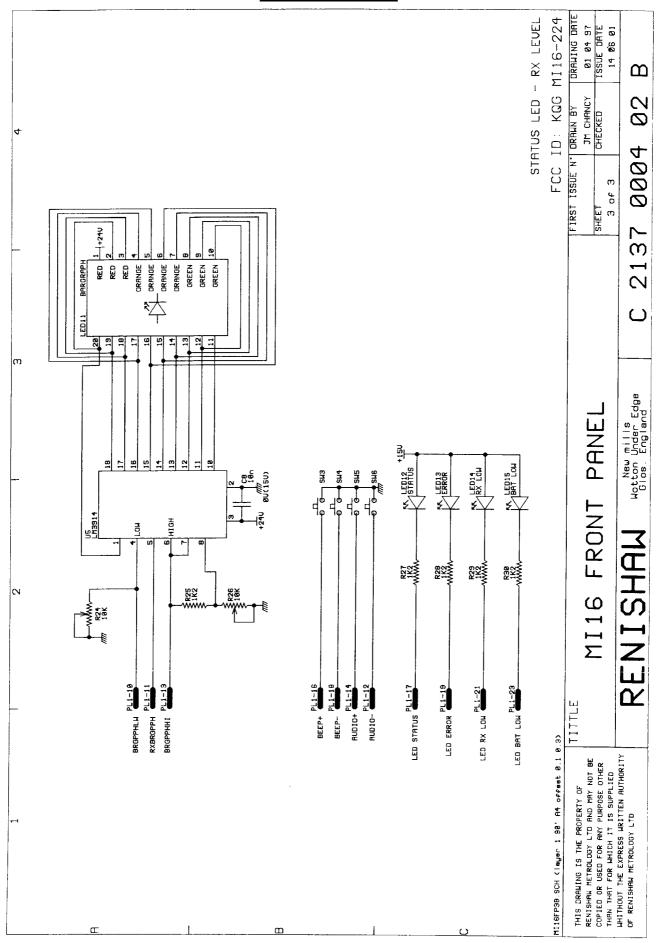

## **DOSSIER DES SCHEMAS CONSTRUCTEUR**

### Contenu du dossier :

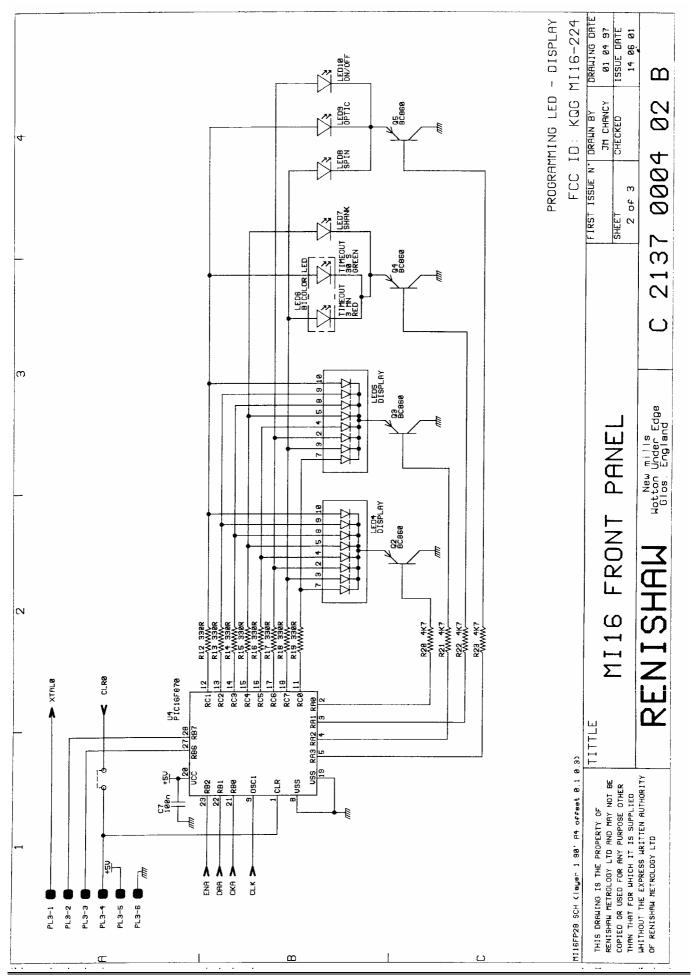

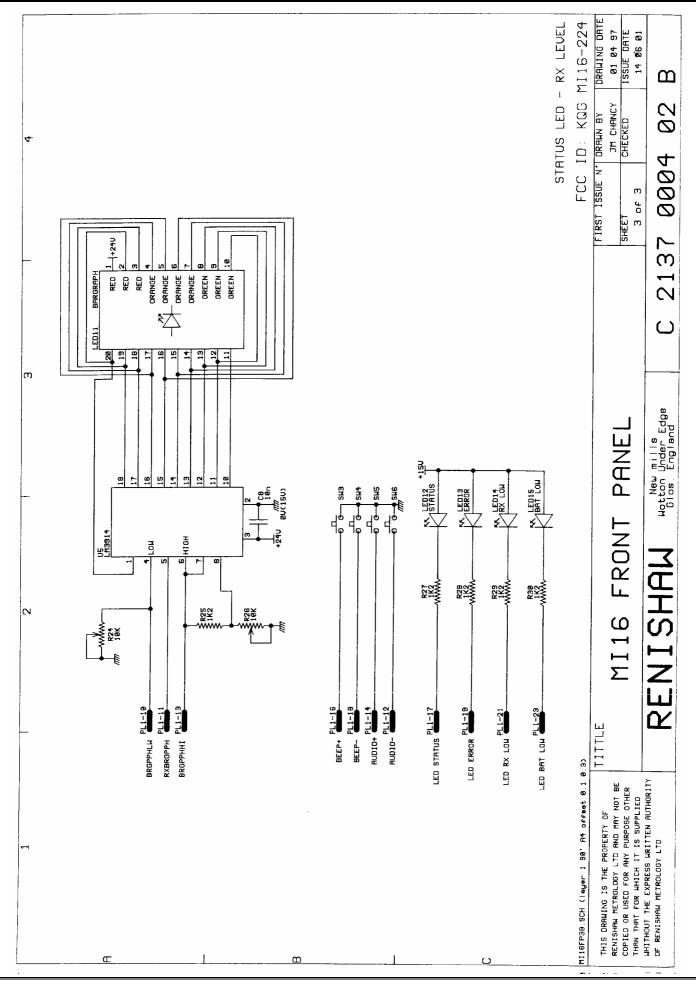

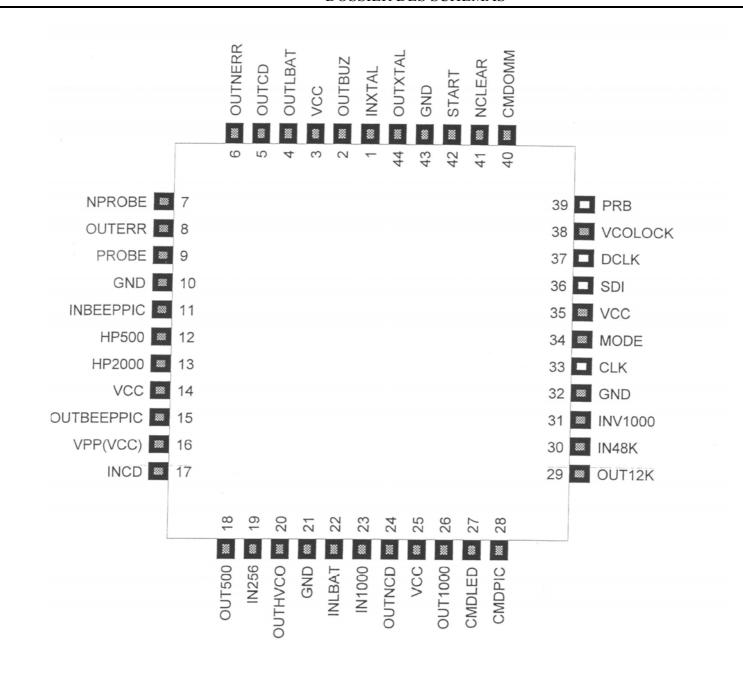

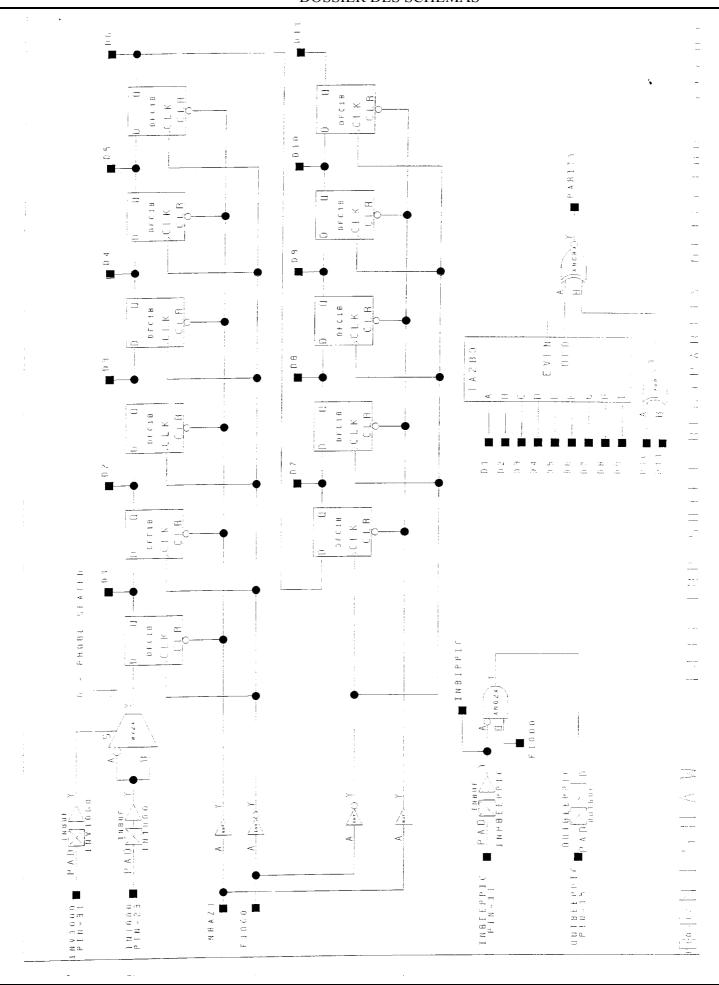

| Schémas partiels de la carte principale du récepteur "MI16 LOGIC PWB" (12 pages)  | 1 à 12  |

|-----------------------------------------------------------------------------------|---------|

| Schémas de la carte face avant du récepteur "MI16 FRONT PANEL" (7 feuilles A4)    | 13 à 15 |

| Schémas partiels des fonctions internes du circuit logique programmable (7 pages) | 16 à 22 |

Page 12

Page 14

# SYSTEME DE PALPAGE A TRANSMISSION RADIO ETUDE DU RECEPTEUR (MI16)

## **DOSSIER DES DOCUMENTATIONS RESSOURCE**

### Contenu du dossier :

| Programme Afficheur (2 pages)         | 1 à 2   |

|---------------------------------------|---------|

| Mémo VHDL (4 pages)                   | 3 à 6   |

| Exemples de programmes VHDL (2 pages) | 7 à 8   |

| PIC16F870 (27 pages)                  | 9 à 35  |

| RB751V-40 (1 page)                    | 36      |

| MC14499 (2 pages)                     | 37 à 38 |

| NE571 (2 pages)                       | 39 à 40 |

| NOTE D'APPLICATION NE571 (4 pages)    | 41 à 44 |

| MF10 (8 pages)                        | 45 à 52 |

| TLC555 (4 pages)                      | 53 à 56 |

| MC1413 (1 page)                       | 57      |

| DOCUMENTATION RELAIS (2 pages)        | 58 à 59 |

| SA601 (6 pages)                       | 60 à 66 |

| FILTRES HELICOIDAUX (2 pages)         | 67 à 68 |

| HC4046 (7 pages)                      | 69 à 75 |

| LF398A (6 pages)                      | 76 à 81 |

| ; PIC 16F870                                                    |               |                |              |                                        |    |          |        |                     |                                         |

|-----------------------------------------------------------------|---------------|----------------|--------------|----------------------------------------|----|----------|--------|---------------------|-----------------------------------------|

| -                                                               | =====         | title          | e "mc14499 ( | du 16 Novembre 2001"                   |    |          |        |                     |                                         |

| ; Le bu                                                         | ut est de rem | placer         | le MC14499   | qui est obsolète. La                   |    |          |        |                     |                                         |

| seule différence est la vitesse de transmission                 |               |                |              |                                        |    |          |        |                     |                                         |

| ; qui a été ralentie dans le programme MI16.                    |               |                |              |                                        | 44 |          | org    | 4                   |                                         |

| ; Il est très important que le clear watch dog (clrwdt) soit en |               |                |              |                                        |    |          | 0.9    | •                   |                                         |

| interruption car dans le pg principal,                          |               |                |              |                                        | 45 |          | movwf  | wbuff               |                                         |

|                                                                 |               |                |              | reset après avoir envoyé               | 46 |          | swapf  | STATUS,w            |                                         |

|                                                                 | arasites avec |                |              | reset apres avoir envoye               | 47 |          | clrf   | STATUS              |                                         |

| des po                                                          | arasites avec | allum          | le gaz:      |                                        | 47 |          | CITT   |                     |                                         |

| //*I                                                            |               | INIC"          |              |                                        | 40 |          |        | ;put in bank0 if i  | necessary                               |

| #inciu                                                          | ıde "P16F870  | .INC           |              |                                        | 48 |          | movwf  | statbuff            |                                         |

|                                                                 |               |                |              |                                        |    |          |        |                     |                                         |

| ;*****                                                          |               |                | "***** Head  | der ***********                        | 49 |          | btfsc  | INTCON,TOIF         |                                         |

| 1                                                               | POINTER       | ₹              | equ          | H'00'                                  | 50 |          | goto   | timeri              |                                         |

|                                                                 |               |                |              |                                        | 51 |          | btfsc  | INTCON,INTF         |                                         |

| 2                                                               | ZERO          | equ            | H'7E'        |                                        | 52 |          | goto   | clki                |                                         |

| 3                                                               | ONE           | equ            | H'oC'        |                                        | 53 |          | movlw  | B'11111000'         |                                         |

| 4                                                               | TWO           | equ            | H'B6'        |                                        | 54 |          | andwf  | INTCON              |                                         |

| 5                                                               | THREE         | equ            | H'9E'        |                                        | 55 |          | goto   | endinter            |                                         |

| 6                                                               | FOUR          | equ            | H'CC'        |                                        | 56 | timeri   | clrwdt | CHAILIC             |                                         |

| 7                                                               | FIVE          | equ            | H'DA'        |                                        | 57 | cirrieri | movlw  | tmrOdiv             |                                         |

|                                                                 |               | •              |              |                                        |    |          |        |                     |                                         |

| 8                                                               | SIX           | equ            | H'FA'        |                                        | 58 |          | movwf  | TMRo                |                                         |

|                                                                 |               |                |              | ng of segments for                     | 59 |          | bsf    | intflg,0            |                                         |

|                                                                 |               |                |              | (PORTC)                                | 60 |          | bcf    | INTCON,TOIF         |                                         |

| 9                                                               | SEVEN         | equ            | H'oE'        |                                        |    |          |        | ;indique au prog    | ramme                                   |

| 10                                                              | EIGHT         | equ            | H'FE'        |                                        |    |          |        | principal l'interru | ption                                   |

| 11                                                              | NINE          | equ            | H'DE'        |                                        | 61 |          | goto   | endinter            |                                         |

| 12                                                              | Α             | equ            | H'EE'        |                                        | 62 | clki     | bcf    | INTCON,INTF         |                                         |

| 13                                                              | i             | equ            | H'60'        |                                        | 63 |          | btfsc  | PORTB,enable        |                                         |

| 14                                                              | iı            | equ            | H'6C'        |                                        | 64 |          | goto   | endinter            |                                         |

|                                                                 | Ü             | •              | H'7C'        |                                        |    |          | bcf    | STATUS,C            |                                         |

| 15                                                              |               | equ            |              |                                        | 65 |          |        | •                   |                                         |

| 16                                                              | DASH          | equ            | H'80'        |                                        | 66 |          | btfsc  | PORTB,datas         |                                         |

| 17                                                              | BLANK         | equ            | H'00'        |                                        | 67 |          | bsf    | STATUS,C            |                                         |

|                                                                 |               |                |              |                                        | 68 |          | rlf    | mode                |                                         |

| ; CON                                                           | ISTANTS       |                |              |                                        | 69 |          | rlf    | bcddigit            |                                         |

| 18                                                              | tmrOdiv       | equ            | D'78'        |                                        | 70 |          | rlf    | poindec             |                                         |

| 19                                                              | datas         | equ            | D'01'        | ; data signal                          | 71 | endinter | swapf  | statbuff,w          |                                         |

| 20                                                              | enable        | equ            | D'02'        | ; enable signal                        | 72 |          | movwf  | STATUS              |                                         |

|                                                                 | 0             | <b>0 4 1 .</b> |              | , спасте я.д.та.                       | 73 |          | swapf  | wbuff               |                                         |

| . UAI                                                           | RIABLES       |                |              |                                        | 74 |          | swapf  | wbuff,w             |                                         |

|                                                                 | digit1        | 0011           | H'20'        |                                        | 74 |          | swupi  | wbuii,w             |                                         |

| 21                                                              | aigiti        | equ            |              |                                        | 75 |          |        |                     |                                         |

|                                                                 |               |                | -            | nank or timeout or                     | 75 |          | retfie |                     |                                         |

|                                                                 |               |                | timeout      | 305                                    |    |          |        |                     |                                         |

| 22                                                              | digit2        | equ            | H'21'        |                                        | 76 | START    |        |                     |                                         |

|                                                                 |               |                |              | oin or spin on/off or optic            | 77 |          | bsf    | STATUS,RPO          | ;page 1                                 |

|                                                                 |               |                | or optic     | on/off                                 | 78 |          | movlw  | B'00000110'         |                                         |

| 23                                                              | digit3        | equ            | H'22'        | ; Unité (display)                      | 79 |          | movwf  | ADCON1              |                                         |

| 24                                                              | digit4        | equ            | H'23'        | ; Dizaine (display)                    |    |          |        |                     |                                         |

| 25                                                              | savdig1       | equ            | H'24'        |                                        | 80 |          | bcf    | STATUS.RPO          | ;page 0                                 |

| 26                                                              | _             | -              | H'25'        |                                        | 81 |          | movlw  | 0                   | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

| 27                                                              | _             | equ            | H'26'        |                                        | 82 |          | movwf  |                     |                                         |

| 28                                                              | _             |                | H'27'        |                                        | 83 |          | movwf  | PORTB               |                                         |

| 29                                                              |               | -              | H'28'        |                                        |    |          |        | PORTC               |                                         |

| 29                                                              | display       | equ            |              | la la calta a calatala                 | 84 |          | movwf  | PORIC               |                                         |

|                                                                 |               |                |              | le location - which                    |    |          | 1 (    | CTATUC DD -         |                                         |

|                                                                 |               |                |              | to update                              | 85 |          | bsf    | STATUS,RPO          | ;page 1                                 |

| 30                                                              | count         | equ            | H'29'        | ; loop counter variable                | 86 |          | movlw  | 0                   |                                         |

| 31                                                              | wbuff         | equ            | H'2A'        | ; register save                        | 87 |          | movwf  | TRISA               |                                         |

| 32                                                              | statbuff      | equ            | H'2B'        | ; register save                        | 88 |          | movwf  | TRISC               |                                         |

| 33                                                              | poindec       | -              | H'2C'        | ; point decimal save                   | 89 |          | movlw  | b'00000111'         |                                         |

| 34                                                              | bcddigit      |                | H'2D'        | ; bcd digit save                       | 90 |          | movwf  | TRISB               |                                         |

| 35                                                              | mode          | equ            | H'2E'        | ; mode save                            |    |          |        |                     |                                         |

| 36                                                              | savpoind      |                | H'2F'        | , mode save                            | 91 |          | bsf    | STATUS,RPo          | ingge 1                                 |

|                                                                 |               |                |              |                                        |    |          |        |                     | ;page 1                                 |

| 37                                                              | savbcd        |                | H'30'        |                                        | 92 |          | movlw  | B'00000100'         |                                         |

| 38                                                              | savmode       |                | H'31'        |                                        | 93 |          | OPTION |                     |                                         |

| 39                                                              | edgenab       | equ            | H'32'        |                                        | 94 |          | bcf    | STATUS,RPO          | ;page 0                                 |

| 40                                                              | intflg        | equ            | H'33'        |                                        | 95 |          | movlw  | B'10110000'         |                                         |

|                                                                 |               |                |              |                                        | 96 |          | movwf  | INTCON              |                                         |

| 41                                                              |               | org            | 0            |                                        | 1  |          |        |                     |                                         |

|                                                                 |               | - 3            | -            |                                        |    |          |        |                     |                                         |

| 42                                                              |               | goto           | START        |                                        | 97 |          | movlw  | tmrOdiv             |                                         |

| 43                                                              |               | retlw          | soft_vers    | ion                                    | 98 |          | movwf  | TMRO                |                                         |

| 43                                                              |               | IEUW           | soit_vers    | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 90 |          | movwi  | ININO               |                                         |

|                                                                 |               |                |              |                                        | 00 |          | menter | LI'CC'              |                                         |

|                                                                 |               |                |              |                                        | 99 |          | movlw  | H'FE'               |                                         |

|     |            |       | D OBBIEN DES DOC                 | CIVILLIVII | 111011  | TILDE    | o chez                               |

|-----|------------|-------|----------------------------------|------------|---------|----------|--------------------------------------|

| 100 |            | movwf | display                          | 158        | RTCC_FI | 11       |                                      |

| 100 |            | movwi | азрау                            | 159        | KICC_II | btfss    | intflg,O                             |

| 101 |            | clrf  | edgenab                          | 160        |         | goto     | MAIN                                 |

|     |            |       |                                  |            |         | bcf      | intflg,0                             |

| 102 |            | clrf  | savpoind                         | 161        |         | DCI      | ilitiig,0                            |

| 103 |            |       | h'oF'                            | 163        | CONUE   | T LIEV T | O DICDI AU                           |

| 103 |            | movlw |                                  | 162        | CONVE   |          | O_DISPLAY                            |

| 104 |            | movwf | savdig1                          | 163        |         | movlw    | digit1                               |

| 105 |            | movwf | savdig2                          | 164        |         | movwf    | FSR                                  |

| 106 |            | movwf | savdig3                          |            |         |          | ; put the address of the first digit |

| 107 |            | movwf | savdig4                          |            |         |          | into the FSR to enable POINTER       |

|     |            |       |                                  | 165        |         | movlw    | H'04'                                |

| 108 | MAIN       | btfsc | PORTB,enable                     | 166        |         | movwf    | count                                |

| 109 |            | goto  | nex1                             |            |         |          | ; prepare count variable to          |

| 110 |            | movlw | D'1'                             |            |         |          | loop for all four displays           |

| 111 |            | movwf | edgenab                          | 167        | NEXT_H  | EX       |                                      |

| 112 |            | goto  | AFFICH                           | 168        |         | movfw    | POINTER                              |

| 113 | nex1       | btfss | edgenab,0                        | 169        |         | call     | RETURN_CODE                          |

| 114 |            | goto  | AFFICH                           | 170        |         | movwf    | POINTER                              |

| 115 |            | clrf  | edgenab                          | 171        |         | incf     | FSR,1                                |

|     |            |       | ici, on vient à la remonté de    | 172        |         | decfsz   | count,1                              |

|     |            |       | "enable" (tested)                | 173        |         | goto     | NEXT_HEX                             |

| 116 |            | movfw | mode                             | .,,5       |         | 9010     |                                      |

| .10 |            | moviw | ;çα prend entre 3 et 27 μS       | 174        |         | btfsc    | display,0                            |

| 117 |            | movwf |                                  | 175        |         | goto     | di                                   |

|     |            | movfw | bcddigit                         | 176        |         | movfw    | digit4                               |

| 118 |            |       | _                                |            |         | btfsc    |                                      |

| 119 |            | movwf | savbcd                           | 177        |         |          | savpoind,3                           |

| 120 |            | movfw | poindec                          | 178        |         | addlw    | 1                                    |

| 121 |            | movwf | savpoind                         | 179        | d1      | btfsc    | display,1                            |

| 122 | bcdconv    |       | savmode                          | 180        |         | goto     | d2                                   |

| 123 |            | movwf | savdig2                          | 181        |         | movfw    | digit3                               |

| 124 |            | movlw | H'oF'                            | 182        |         | btfsc    | savpoind,2                           |

| 125 |            | andwf | savdig2                          | 183        |         | addlw    | 1                                    |

| 126 |            | bcf   | STATUS,C                         |            |         |          |                                      |

| 127 |            | rrf   | savmode                          | 184        | d2      | btfsc    | display,2                            |

| 128 |            | bcf   | STATUS,C                         | 185        |         | goto     | d3                                   |

| 129 |            | rrf   | savmode                          | 186        |         | movfw    | digit2                               |

| 130 |            | bcf   | STATUS,C                         | 187        |         | btfsc    | savpoind,1                           |

| 130 |            | rrf   | savmode                          | 188        |         | addlw    | 1                                    |

| 131 |            | bcf   | STATUS,C                         | 189        | d3      | btfsc    | display,3                            |

| 132 |            | rrf   | savmode                          | 190        | us      | goto     | dsp                                  |

|     |            | movfw | savmode                          |            |         | movfw    | digit1                               |

| 133 |            |       |                                  | 191        |         |          |                                      |

| 134 |            | movwf | savdig1                          | 192        |         | btfsc    | savpoind,0                           |

| 425 |            |       | and and                          | 193        | .1      | addlw    | 1<br>PODTS                           |

| 135 |            | movfw | •                                | 194        | dsp     |          | PORTC                                |

| 136 |            | movwf | savdig3                          | 195        |         | movfw    | display                              |

| 137 |            | movlw | H'oF'                            | 196        |         | movwf    | PORTA                                |

| 138 |            | andwf | savdig3                          | 197        |         | movwf    | display                              |

| 139 |            | bcf   | STATUS,C                         | 198        |         | rlf      | display,1                            |

| 140 |            | rrf   | savbcd                           | 199        |         | bsf      | display,0                            |

| 141 |            | bcf   | STATUS,C                         | 200        |         | btfss    | display,4                            |

| 142 |            | rrf   | savbcd                           | 201        |         | bcf      | display,0                            |

| 143 |            | bcf   | STATUS,C                         | 202        |         | goto M   | IAIN                                 |

| 144 |            | rrf   | savbcd                           |            |         |          |                                      |

| 145 |            | bcf   | STATUS,C                         | 203        | RETURN  | LCODE    |                                      |

| 146 |            | rrf   | savbcd                           | 204        |         | addwf    | PCL,1                                |

| 147 |            | movfw | savbcd                           | 205        |         | retlw    | ZERO                                 |

| 148 |            | movwf | savdig4                          | 206        |         | retlw    | ONE                                  |

|     |            |       | 20.00.3                          | 207        |         | retlw    | TWO                                  |

| 149 | AFFICH     |       |                                  | 208        |         | retlw    | THREE                                |

| 150 | A. 1 IOI I | movfw | savdig1 ;dizaine (voir code aff) | 209        |         | retlw    | FOUR                                 |

| 151 |            | movwf | digit1                           | 210        |         | retlw    | FIVE                                 |

|     |            | movfw | savdig2 ;unité (voir code aff)   | 210        |         | retlw    | SIX                                  |

| 152 |            |       |                                  |            |         |          |                                      |

| 153 |            | movwf | digit2                           | 212        |         | retlw    | SEVEN                                |

| 154 |            | movfw | savdig3 ;unité                   | 213        |         | retlw    | EIGHT                                |

| 155 |            | movwf | digit3                           | 214        |         | retlw    | NINE                                 |

| 156 |            | movfw | savdig4 ;dizaine                 | 215        |         | retlw    | A                                    |

| 157 |            | movwf | digit4                           | 216        |         | retlw    | 1                                    |

|     |            |       |                                  | 217        |         | retlw    | II                                   |

|     |            |       |                                  | 218        |         | retlw    | U                                    |

|     |            |       |                                  | 219        |         | retlw    | DASH                                 |

|     |            |       |                                  | 220        |         | retlw    | BLANK                                |

|     |            |       |                                  | 221        | END     |          |                                      |

|     |            |       |                                  |            |         |          |                                      |

Instructions concurrentes

## VHDL: du Langage à la Modélisation R. Airiau / J.M. Bergé / V. Olive / J. Rouillard

Photocopie de cette page autorisée par les auteurs sous réserve de la présence de cette mention

#### Instructions séquentielles

#### -- Instruction processus (label :) process -- Affectation de variables -- Déclarations VAR2 := VAR1 / (VAR3 + VAR4); begin MON\_POINTEUR := new INTEGER'(3); -- Instructions séquentielles TAB(1 to 3) := (1,2,3); {wait on liste\_des\_signaux\_surveillés;} -- Instruction conditionnelle end process (label); if condition booléenne 1 then -- Traitement 1. elsif condition\_booléenne\_2 then -- Traitement 2. -- Affectation de formes d'ondes A <= B after 10 ns, '1' after 20 ns: else -- Traitement 3. (A,B) <= transport (BLEU, '1') after 10 ns; end if: -- Instruction de bloc -- Instruction de choix label: block {(CLK='1' and not CLK'STABLE)} case expression is {en-tête\_généricité\_et\_ports} when Valeur\_1 => -- Instructions\_1 -- Déclarations locales when Valeur\_2 | Valeur\_3 => -- Instructions\_2 when Valeur\_4 to Valeur\_5 => -- Instructions\_3 -- Instructions concurrentes Valeur\_6 downto Valeur\_8 =>-- Instructions\_4 end block {label}; when others => -- Instructions N -- Affectation conditionnelle de signaux end case ; If CONDITION then SIGNAL1 <= {transport} '0'; -- Instruction de boucle { elsif CONDITION\_2 then { label : } loop... -- Instructions séquentielles $(A1, A2) \le \{transport\} ('1', "010") \{after 10 ns; \}$ end loop { label }; { label : } for indice in Intervalle loop nom\_ou\_agrégat <= {transport} forme d'onde n ;} ... -- Suite d'instructions séquentielles end if: end loop { label } ; { label\_de\_boucle : } while condition loop -- Affectation d'un signal selectionné ... -- Suite d'instructions séquentielles {label :} with CHOIX select next { label\_de\_boucle } { when condition} ; nom\_ou\_agrégat <= {guarded} {transport} end loop { label\_de\_boucle }; "1000" when "01", exit { label\_de\_boucle } { when condition} ; "0100" when "10", ... forme\_d'onde\_n when choix\_n, null: -- Instruction nulle { nom\_ou\_agrégat when others}; return VALEUR: -- Retour de fonction -- Appel de procédure -- Appel de sous-programmes VERIFICATION\_HOLD(SIGNAL1, 3 ns); MA PROCEDURE (NBR, MESSAGE => "GO"); VALEUR := FONCT1( TAB'LOW, 'A', VAR2); -- Instruction d'assertion assert condition\_booléenne {report message} {severity NOTE | WARNING | ERROR | FAILURE} ; -- Affectation de formes d'ondes B <= transport ENTREE, null after 10 ms; -- Instanciation de composants S <= B after 10 ns, '1' after 20 ns; C1: INVERSEUR port map (E => A, S=> B); C2: INVERSEUR -- Instruction d'attente { generic map ( 10 ns ) } wait on {liste\_de\_signaux} { until condition } port map (C, D); for expression\_de\_temps); Instruction de génération -- Instruction d'assertion LABEL: if CONDITION generate assert condition booléenne (report message) (severity NOTE | WARNING | ERROR Ensemble d'instructions concurrentes end generate { LABEL } ; FAILURE); LABEL: for PARAMETRE in INTERVALLE -- La spécification d'attributs donne une generate -- valeur à ceux-ci -- Ensemble d'instructions concurrentes

MEMO VHDL Page 3

attribute NBR\_PATTES of C1: component is 32; end generate { LABEL };

## VHDL : du Langage à la Modélisation R. Airiau / J.M. Bergé / V. Olive / J. Rouillard

Photocopie de cette page autorisée par les auteurs sous réserve de la présence de cette mention

#### Déclarations de types

### type COULEUR is (VERT, BLEU, JAUNE);

Type tableau non contraint

type VECTEUR\_D\_ENTIERS is array (POSITIVE range <>) of INTEGER;

Type tableau contraint

type TABLEAU is array (1 to 10) of INTEGER;

type FLOT is range 1.00 to 2.00;

Déclaration incomplète de type

type ARTICLE;

-- Type pointeur

type ACCES is access ARTICLE;

Type enregistrement

type ARTICLE is record

NUMERO: INTEGER; VALEUR: FLOAT:

SUIVANT: ACCES:

end record:

- -- Sous-type associé

- -- à une fonction de résolution

subtype SOUS\_TYPE

is { FONCTION\_DE\_RESOLUTION}

TYPE\_DE\_BASE { contraintes};

Type physique

type DISTANCE is range 0 to 1E16

units

-- Angstrom

10 A; -- nanomètre

end units;

-- Type fichier

type FICHIER\_DE\_BIT is file of BIT;

#### Déclarations d'objets

constant PI: REAL:= 3.1416; constant DIFFEREE: INTEGER;

variable NOM: TYPE\_OU\_SOUS-TYPE { := VALEUR\_D'INITIALISATION } ;

constant LOCALE : BIT := FCT\_INIT ( P1) ;

file FICHIER : TYPE\_DU\_FICHIER is { in | out } -- Déclaration de procédure destinée à être

NOM\_LOGIQUE\_DU\_FICHIER;

signal CE\_SIGNAL : { FCT\_DE\_RESOLUTION}

TYPE\_OU\_SOUS-TYPE { contraintes} {register/bus} {:= VALEUR\_INITIALE} ;

attribute NOM\_DE\_L\_ATTRIBUT : BOOLEAN ;

attribute NOM: STRING;

alias BIT4: BIT is VECTEUR (4);

alias PAGE: BIT\_VECTOR(1 to 2) is

ADRESSE(16 downto 15);

component COMPOSANT

{ generic ( DELAIS : TIME := 0 ns;

N: POSITIVE;...);}

{ port (ENTREE : in VECTOR (1 downto N);... );} function RESOLUTION ( V : in BIT\_VECTOR)

end component;

### Déclarations et spécifications

| Déclarations<br>autorisées<br>(ou impossibles) | Spécification d'entité | Architecture | Configuration | Spec. de paquetage | Corps de paquetage | Bloc | Process | Sous-programmes |

|------------------------------------------------|------------------------|--------------|---------------|--------------------|--------------------|------|---------|-----------------|

| Déclaration de sous-programme                  | oui                    | ouf          | 1111          | out                | out                | oui  | out     | ou              |

| Corps de sous programme                        | out                    | oui          | 1111          | 1111               | oui                | oui  | out     | ou              |

| Déclaration de type                            | out                    | out          | 1111          | out                | oui                | oui  | ouf     | ou              |

| Déclaration de sous type                       | out                    | out          | 111           | out                | out                | oul  | υu!     | ou              |

| Déclaration de constante                       | out                    | oui          | 1111          | out                | out                | ouf  | oui     | ou              |

| Déclaration de variable                        |                        | III          | III           |                    | 111                | 1111 | ouf     | ou              |

| Déclaration de signal                          | out                    | ouf          | 1111          | oui                | 111                | oui  | 111     |                 |

| Déclaration de fichier                         | oui                    | out          | 1111          | oui                | oui                | oui  | out     | ou              |

| Déclaration d'altas                            | oui                    | oul          | 1111          | out                | oui                | out  | out     | ou              |

| Déclaration de composant                       |                        | ouf          | 1111          | oui                |                    | oui  |         |                 |

| Déclaration d'attribut                         | ouf                    | oui          | 111           | oui                |                    | out  | out     | ou              |

| Spécification d'attribut                       | out                    | out          | out           | ouf                |                    | out  | out     | ou              |

| Spécification de déconnection                  | ouf                    | ouf          | 111.          | out                | III.               | ouf  |         |                 |

| Spécification de configuration                 | 1111                   | out          | 111           | 111                | 111                | out  | III     | 111             |

| Déclaration d'entité                           |                        | 111.         | 111           |                    | 111                | 1111 | 111     |                 |

| Déclaration de configuration                   |                        | 111          |               |                    | 111                | III  |         |                 |

| Déclaration de paquetage                       |                        |              | 111           | III                | III                | III  | III     |                 |

| Clause use                                     | out                    | oui          | out           | out                | oui                | out  | out     | ou              |

### Déclarations de sous-programmes

Déclaration de procédures

procedure CAN { ( ENTREE : { in} REAL {:= 0.0};

SORTIE: out INTEGER;

CONTROLE :inout BOOLEAN; ...)];

- -- appelée dans un ensemble d'instructions

- -- concurrentes

procedure VERIFICATION ( NOM : { in } STRING:

signal S: { in} INTEGER);

-- Déclaration de fonctions

function MIN {(A: {in} } REAL:

B: { in } REAL) } return REAL;

-- Surcharge de la fonction "+"

function "+" (A, B: VOLT) return VOLT;

return BIT:

MEMO VHDL Page 4

## VHDL: du Langage à la Modélisation R. Airiau / J.M. Bergé / V. Olive / J. Rouillard

Photocopie de cette page autorisée par les auteurs sous réserve de la présence de cette mention

#### Déclarations d'entités

### Corps d'architecture

#### architecture MODEL of ADD is

- -- Clause use éventuelles

- -- Déclarations de types, de constantes

- -- d'objets (mais pas de variables), de composants,

- -- de sous-programmes et d'attributs .

- -- Spécifications de corps de sous-programmes,

- -- d'attributs, de configurations et de déconnexion

#### begin

-- Instructions concurrentes

end { MODEL };

#### Déclaration de paquetages

```

{ library LIB; }

{ use LIB; }

package P1_PKG is

-- Clauses use éventuelles

-- Déclarations de types, d'attributs, d'objects

-- (sauf des variables) et de composants

-- Spécifications d'attributs et de déconnexions

constant NOM: STRING;

type L3 is ('0', '1', 'Z');

function "+" ( A1, A2: in L3) return L3;

procedure ETAT_SUITE

({ variable } ETAT: inout TIME;

signal S: in L3; signal ENABLE: out L3);

end { P1_PKG };

```

#### Spécification de déconnexion

```

disconnect S1_GARDE, S2_GARDE: BIT4

after 1 ms;

disconnect others: BIT4 after 500 us;

disconnect all: TYPE_ADRESSE after 50 us;

```

# Corps de paquetages et de sous-programmes

```

{ library LIB1; }

{ use LIB1.P2_PKG.all; }

package body P1_PKG is

-- Clauses use éventuelles.

-- Déclarations de types, d'objets (sauf variables),

-- de sous-programmes. Corps de sous-programmes

constant NOM: STRING:= "P1_PKG";

function "+" (A1, A2: in L3) return L3 is

... begin ... return V3; ... end "+";

procedure ETAT_SUITE

({ variable} ETAT: inout TIME;

signal S: in L3; signal ENABLE: out L3) is ...

end P1_PKG;

```

### Spécification de configurations

```

for C1, C2: COMPOSANT_C use open { generic map ( 10 ns , "Ci") { port map (E => F1(ENTREE), F2(S) => SORTIE) } ; for all : COMPOSANT_C2 use entity WORK.INVERSEUR ( A1 ) ; for C3: COMPOSANT_C use entity WORK.E1 (A3) ; for others: COMPOSANT_C use configuration WORK.CONF1;

```

### Configurations

```

library WORK:

library LIB1:

configuration C1 of WORK.ENT1 is

-- specification d'attributs

-- clause use

for ENT1_BLOC -- configuration de bloc

for C1: REGISTRE use entity LIB1.U1 (A2)

{ generic map (3 \text{ ns}, N \Rightarrow 8) };

for A2 -- configuration de generate

for all: REG_BIT use entity LIB1.R1 (A1);

end for

end for ; -- A2

end for ;-- Cl

for DATA: BUS_DONNEE use LIB2.D_BUS (A1)

port map (S_IN => SIN;

S OUT => SOUT:

ERROR => ERR);

end for ; -- DATA

for HORLOGE: CLOCK_G use configuration

WORK.HORLOGE_CONF;

end for ; -- HORLOGE ;

end for ; -- ENT1_BLOC

end { C1 };

```

MEMO VHDL Page 5

## VHDL: du Langage à la Modélisation R. Airiau / J.M. Bergé / V. Olive / J. Rouillard

Photocopie de cette page autorisée par les auteurs sous réserve de la présence de cette mention

#### Visibilité des identificateurs

- -- Clause de référence à une bibliothèque. library STD\_LIB ;

- -- WORK et STD sont deux bibliothèques

- -- prédéfinies, la clause library WORK, STD;

- -- précède implicitement chaque unité. WORK

- -- contient les paquetages: STANDARD et TEXTIO .

- -- Rend visible l'unité UAL de la

- -- bibliothèque STD LIB.

use STD\_LIB.UAL;

- -- Rend visible toutes les unités

- -- de la bibliothèque STD\_LIB.

use STD\_LIB.all;

- -- Rend visible le paquetage P1\_PKG défini

- -- dans la bibliothèque STD\_LIB.

use STD\_LIB.P1\_PKG;

- -- Tous les noms du paquetage P1\_PKG

- -- sont visibles

use P1\_PKG.all;

- -- Les déclarations contenues dans le paquetage

- -- STANDARD sont visibles, une clause use

- -- STD.STANDARD.all; précède implicitement

- -- chaque unité.

#### Spécification d'attributs

attribute NOM\_ATTRIBUT of

NOM\_ENTITE | others | all : entity

- | architecture | configuration | procedure

- | function | package | type | subtype

- I constant | signal | variable | component

- I label is VALEUR ATTRIBUT :

attribute NIVEAU of C1, C2: label is 2

attribute NIVEAU of others: label is 0;

attribute SIMULATION of all: signal is CMOS;

attribute TOPOLOGIE of S1: signal is NORD;

attribute forotogic of SI . signal is NORD

${\bf attribute} \ VALEUR\_T0 \ {\bf of} \ F1: {\bf function} \ {\bf is} \ 10 \ ;$

attribute VERSION of C1: component is "FIRST";

### Référence d'attributs

N := C1'NIVEAU; if F1'REFLEXIVE then ... for I in A'RANGE loop ... ECRIRE ( C1'GENERATION );

### Attributs prédéfinis

- •S'QUIET { (T) } Signal, TRUE si S est tranquile pendant T au moins.

- •STRANSACTION Signal BIT, '1' si S est actif

- •S'STABLE { (T) } Signal, TRUE si aucun événement sur S depuis T

- •S'DELAYED { (T) } Signal S différé de T après NOW

- •S'ACTIVE Fonction, TRUE si S est actif

- •S'LAST\_ACTIVE Valeur du temps écoulé depuis que S fût actif

- •S'EVENT Fonction booléenne, TRUE

si un événement vient d'arriver sur S

- •S'LAST\_VALUE Dernière valeur de S avant le dernier événement

- •S'LAST\_EVENT Valeur du temps écoulé depuis le dernier événement de S

- •T 'BASE Type de base de T

- •T 'LEFT Limite gauche de T

- •T 'RIGHT- Limite droite de T

- •T 'HIGHT La plus haute limite de T

- •T 'LOW La plus basse limite de T

- •T 'POS (X) Position de X dans le type de base de T

- •T VAL (X) -Valeur du X ème élément de T

- •T 'SUCC (X) =T 'VAL (T 'POS (X) + 1)

- •T 'PRED (X) =T 'VAL (T 'POS (X) 1)

- •T 'LEFTOF ( X ) = T ' PRED ( X ) si T est croissant, T 'SUCC ( X ) sinon

- •T'RIGHTOF (X) = T 'SUCC (X) si T est croissant, T 'PRED (X) sinon

- •A'LEFT { ( N ) } Limite gauche du

- N ième index de A

•A'RIGHT { ( N ) } Limite droite du

- N ième index de A

- •A'LOW { (N) } Plus basse limite du

- N tême today de A

- N ième index de A

- •A'HIGH { (N) } Plus haute limite du

- N ième index de A

- •A'LENGTH { ( N ) } Longeur de A, N ème index

- •A'RANGE { ( N ) } Variation du N ième index

- •A'REVERSE\_RANGE { ( N ) } Variation inverse du N ième index

- •B'BEHAVIOR FALSE si B contient

l'instanciation d'un composant

•B'STRUCTURE - TRUE si B ne contient

aucune affectation de signaux

Page 6 MEMO VHDL

```

DECODEUR BCD VERS 7 SEGMENTS ANODES COMMUNES

entrée "val" valeur BCD sur 4 bits

-- sorties "SEG" 7 segments

library ieee;

use ieee.std_logic_1164.all; -- type std_logic

entity decode is

port( val:in std_logic_vector (3 downto 0);

-- 7 => A;...;

SEG:out std_logic_vector(7 downto 1)); -- 1 => G

end decode;

architecture arch of decode is

begin

process(val)

begin

case val is

when "0000" \Rightarrow SEG<="0000001";

when "0001" => SEG<="1001111";

when "0010" => SEG<="0010010";

when "0011" \Rightarrow SEG<="0000110";

--e

when "0100" => SEG <= "1001100";

when "0101" => SEG <= "0100100";

when "0110" => SEG <= "0100000";

when "0111" => SEG<="0001111";

when "1000" => SEG<="0000000";

when "1001" => SEG<="0000100";

when others => SEG<="11111111";

end case;

end process;

end arch;

```

```

--

COMPTEUR DECOMPTEUR DECIMAL

entrées : "h" signal d'horloge, "raz" remise à zéro du compteur,

"ud" commande de comptage décomptage (ud=1 => comptage)

sorties "s" 4 bits binaire codé en décimal

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity compd is

port (h,raz,ud:in STD_LOGIC;s:out STD_LOGIC_VECTOR(3 downto 0));

end compd;

architecture compd_arch of compd is

signal temp : STD_LOGIC_VECTOR(3 downto 0);

begin

process (h,raz)

begin

if raz='1' then temp<="0000";

elsif h'event and h='1' then

if ud='1' and temp="1001" then temp<="0000";

elsif ud='1' then temp<=temp+'1';

elsif ud='0' and temp="0000" then temp<="1001";

else temp<=temp-'1';

end if;

end if;

end process;

s<=temp;

end compd_arch;

```

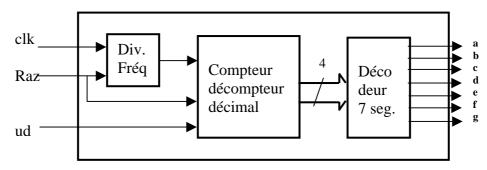

"Composant" qui, à partir d'un signal d'horloge à 8,... MHz, d'un signal de remise à zéro et d'un signal de comptage décomptage, nous permet d'incrémenter ou de décrémenter les valeurs de 0 à 9 sur un afficheur sept segments (au rythme d'un changement toutes les ½ secondes environ)

```

-- entrée "clk" pour l'horloge (quartz 8,...MHz)

-- entrée "raz" pour la remise zero du compteur

entrée "ud" pour compter ou decompter (ud=1 --> compte)

sorties "a,b,c,d,e,f,g" pour afficheur 7 segments anodes comm.

-- Composants "compd", "divfreq" et "decode" créés dans d'autres sources VHDL

library ieee;

use ieee.std_logic_1164.all; -- type std_logic

entity compaff is

port(clk,raz,ud:in std_logic;a,b,c,d,e,f,g:out std_logic);

end compaff;

architecture arch of compaff is

component divfreq

port (h: in STD_LOGIC;hbf: out STD_LOGIC);

end component;

component compd

port (h,raz,ud:in STD_LOGIC;s:out STD_LOGIC_VECTOR(3 downto 0));

end component;

component decode

port( val:in std_logic_vector (3 downto 0);

-- 7 => A;...;

SEG:out std_logic_vector(7 downto 1)); -- 1 => G

end component;

signal clk2:std_logic;

signal val:std_logic_vector(3 downto 0);

signal seg:std_logic_vector(6 downto 0);

begin

fp1 : divfreq port map (clk,clk2);

fp2 : compd port map (clk2,raz,ud,val);

fp3 : decode port map (val,seg);

a \le seq(6);

b \le seq(5);

c < = seq(4);

d < = seq(3);

e < = seg(2);

f < = seg(1);

g < = seg(0);

end arch;

```

## DOSSIER DES DOCUMENTATIONS RESSOURCE

Suite à une altération du fichier original, la suite de la documentation figure dans les fichiers :

- Documentations1.zipDocumentations2.zip

# SYSTEME DE PALPAGE A TRANSMISSION RADIO

# ETUDE DU RECEPTEUR (MI16)

# **DOSSIER DE QUESTIONNEMENT**

# Contenu du dossier :

| <b>Partie</b> A | A : Etude fonctionnelle de la partie réception           | 1  |

|-----------------|----------------------------------------------------------|----|

| <b>A.</b> 1     | Principe de la mesure.                                   | 1  |

| A.2             | Signal émis.                                             | 1  |

| A.3             | Structure du récepteur.                                  | 1  |

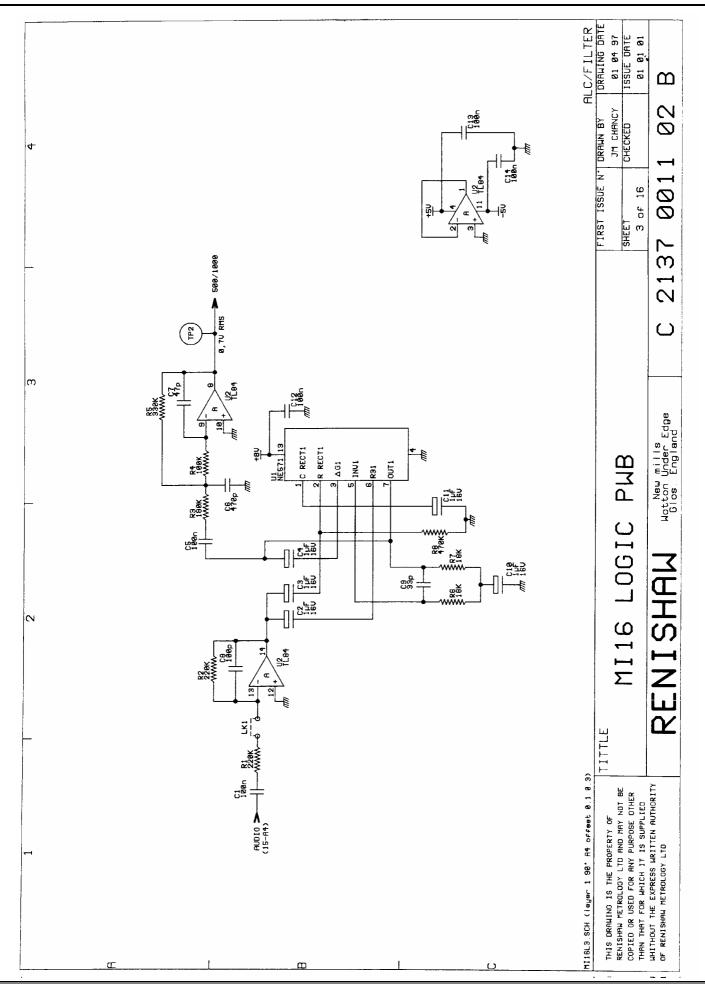

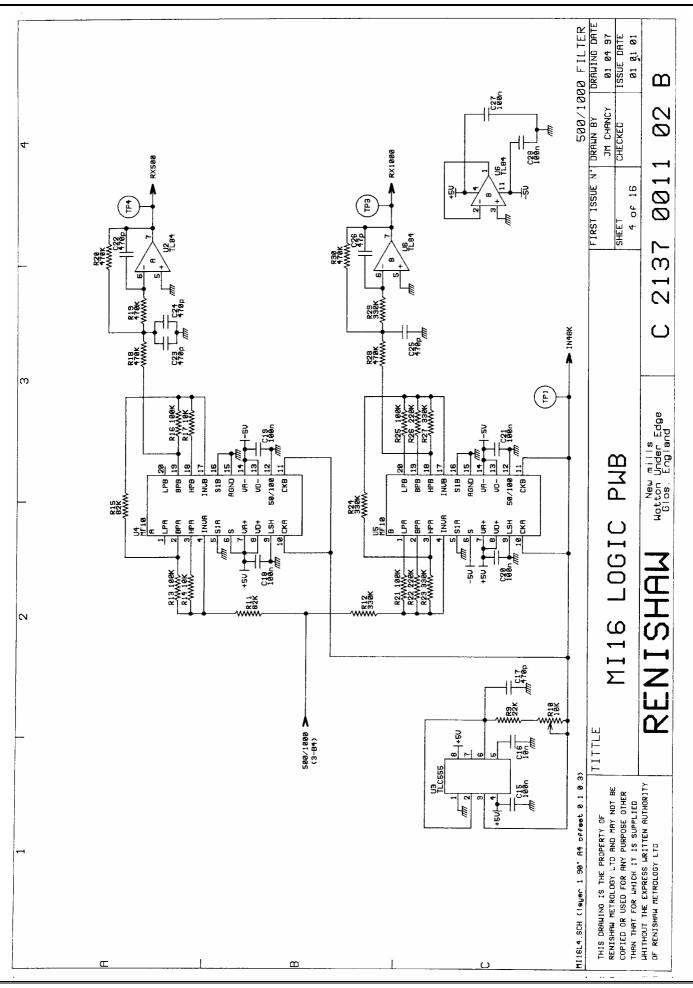

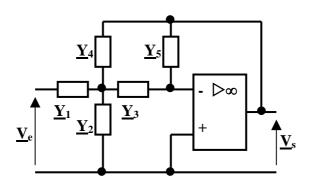

| Partie I        | B : Le filtre ALC et le filtre 500/1000                  | 2  |

| B.1             | Etude préliminaire                                       |    |

| B.2             | Etude du filtre ALC                                      |    |

| B.3             | Etude du filtre 500/1000.                                | 2  |

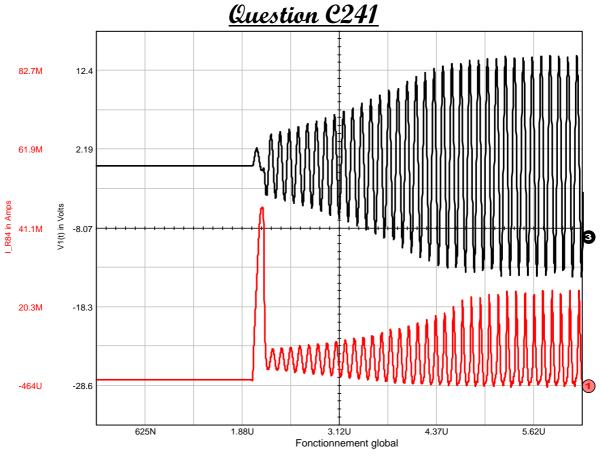

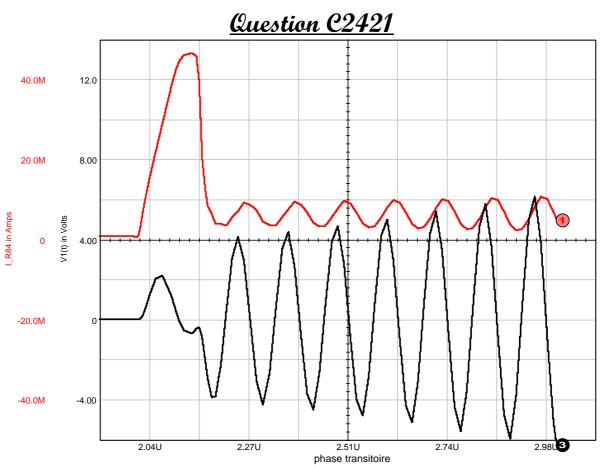

| Partie (        | C : Etude de la structure Led / Relay Driver             | 4  |

| C.1             | Etude fonctionnelle.                                     |    |

| C.2             | Etude structurelle de la partie vue du primaire.         |    |

| C.3             | Formes d'onde et temps de réponse du relais.             |    |

| Partie I        | D : Etude de la carte MI 16 Front Panel                  |    |

| D.1             | Etude Fonctionnelle.                                     |    |

| D.2             | Etude des microcontrôleurs.                              |    |

| D.3             | Etude structurelle de la carte MI16.                     |    |

| D.4             | Etude du programme gérant l'affichage                    |    |

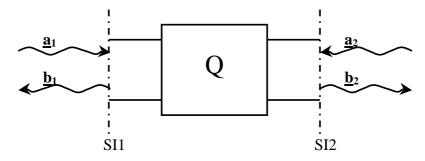

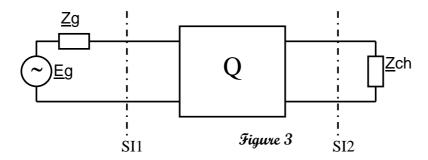

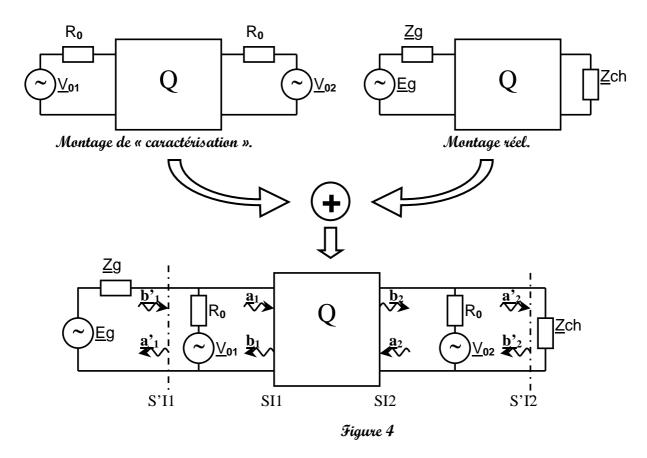

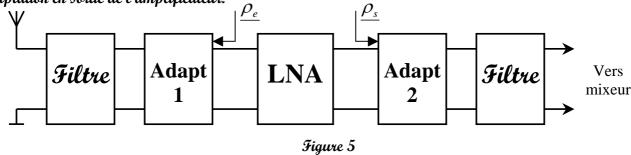

| Partie I        | E : Gain en puissance de l'amplificateur HF              | 13 |

| E.1             | Notion de puissance incidente et de puissance réfléchie. |    |

| E.2             | Paramètres S d'un quadripôle.                            |    |

| E.3             | Identification de l'amplificateur RF.                    |    |

| E.4             | Gain en puissance de l'amplificateur non adapté          |    |

| E.5             | Gain en puissance de l'amplificateur adapté              |    |

| Partie I        | F: Cellules d'adaptation                                 | 17 |

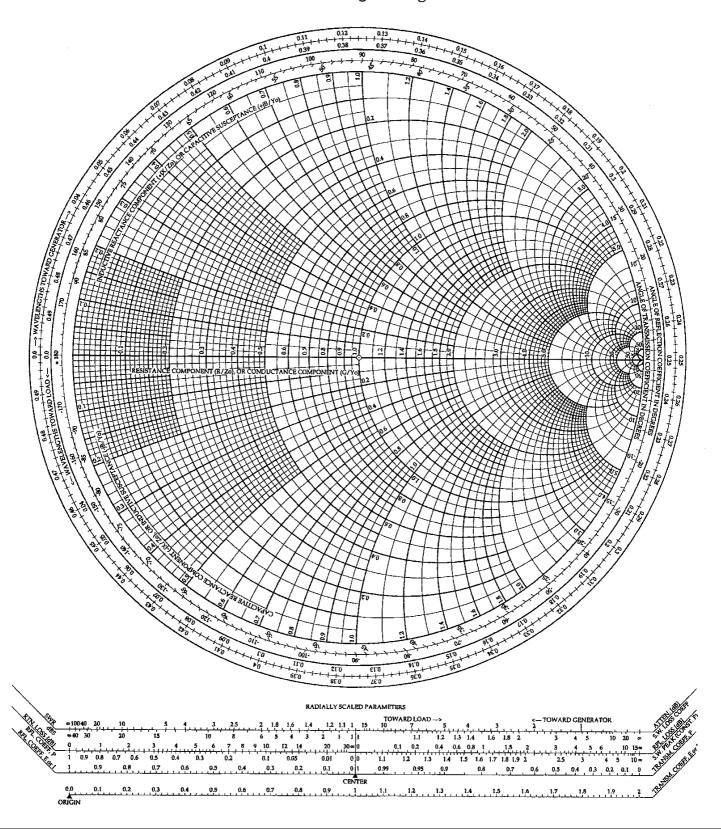

| F.1             | L'outil « abaque de Smith »                              |    |

| F.2             | Adaptation à la sortie du filtre hélicoïdal L4.          |    |

| F.3             | Cellules d'adaptation de l'amplificateur RF.             |    |

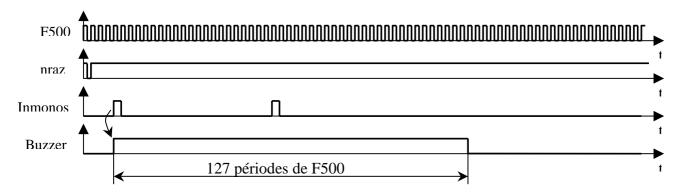

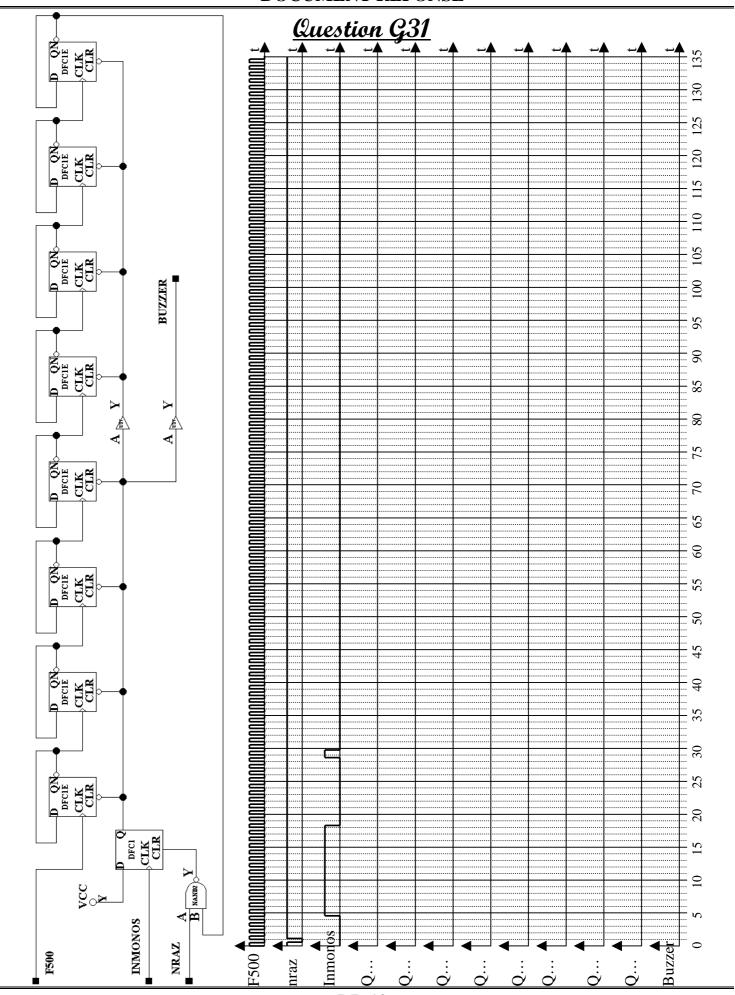

| Partie (        | G : Circuit logique programmable                         | 19 |

| G.1             | Généralités.                                             |    |

| G.2             | Diviseur de fréquence.                                   |    |

| G.3             | Structure monostable.                                    |    |

| G.4             | Réception du mot de 8 bits transmis par l'émetteur.      | 20 |

## Partie A: Etude fonctionnelle de la partie réception.

Avant d'étudier le récepteur proprement dit, il faut comprendre le principe de la mesure et connaître la forme du signal émis.

### A.1 Principe de la mesure.

Pour faire une mesure de distance avec une machine à commande numérique, nous allons utiliser les vitesses d'approche de la machine et mesurer un temps. Les vitesses sont régulées précisément et dans notre cas, on avance de 0.08m/s.

Pour des raisons d'occupation de canal de transmission, le signal utilisé a une fréquence de 1kHz (976Hz en réalité) et est modulé par saut de phase pour pouvoir transmettre une information binaire.

A chaque début de période du IkHz, nous regardons l'état du palpeur pour transmettre une période complète du signal. Si le palpeur n'est pas en contact avec la pièce, nous envoyons un signal en phase et s'il est en contact, un signal en opposition de phase.

**A.1.1** Si on se limite à cette mesure, quelle est la précision obtenue?

Four améliorer la mesure, on décide de mesurer l'instant dans la période considérée où le contact s'est produit. Pour connaître le n<sup>ième</sup> de période, nous utilisons un mot de 8 bits.

a.1.2 Quelle précision atteint-on maintenant? Cela est-il satisfaisant?

### A.2 Signal émis.

- a.2.1 Caractériser le signal présent à la sortie de l'émetteur.

- a.2.2 Quelle est la fréquence d'émission du canal 37, le premier canal étant le canal 0?

## A.3 Structure du récepteur.

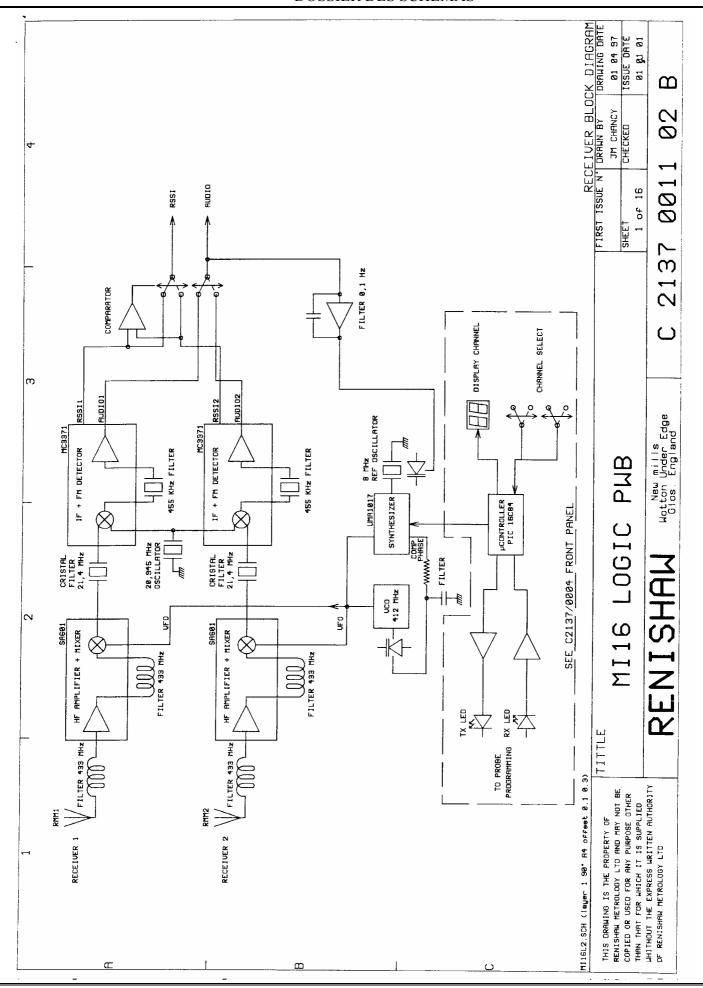

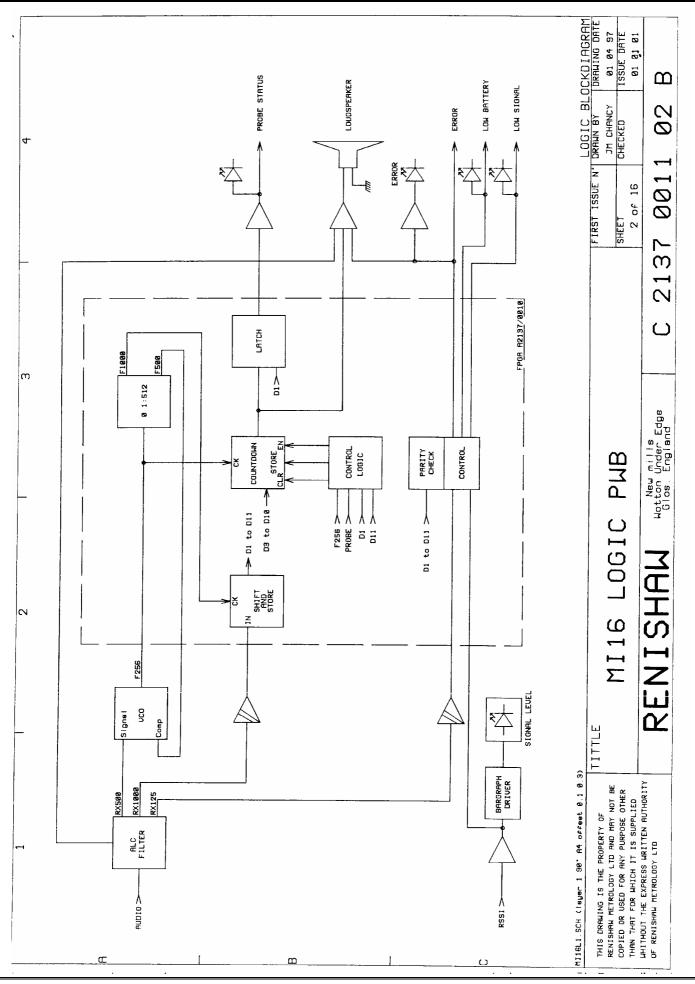

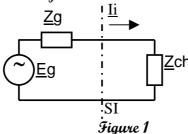

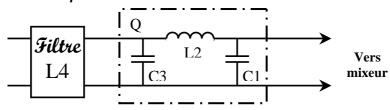

Etude à partir du schéma bloc « MI16 LOGIC PWB 1/16 » page 1 du document schéma.

- A.3.1 Donner le rôle du filtre de 433 Mhz présent en entrée. Quel est le type de filtre utilisé ici?

Le signal est ensuite amplifié et à nouveau filtré avec un filtre hélicoïdal. Nous rencontrons ensuite une structure appelée mixer.