## **AGREGATION INTERNE DE GENIE ELECTRIQUE**

## Option A

## ELECTRONIQUE ET INFORMATIQUE INDUSTRIELLE

Etude d'un système industriel (durée 8 heures)

## PILOTAGE D'UN FOUR ELECTRIQUE A ARC

## **DOCUMENTS CONSTRUCTEUR**

Ce document présente les documentations partielles des composants nécessaires.

| □ OP20     | page 2  | à | page 3  |

|------------|---------|---|---------|

|            | page 4  | à | page 11 |

| □ OP77     | page 12 | à | page 13 |

|            | page 14 | à | page 16 |

|            | page 17 | à | page 19 |

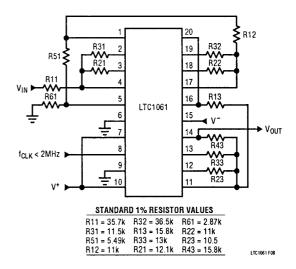

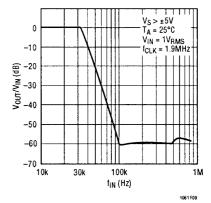

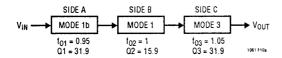

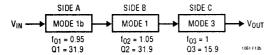

| □ LTC1061  | page 20 | à | page 32 |

| AD536A     | page 33 | à | page 39 |

|            | page 40 | à | page 46 |

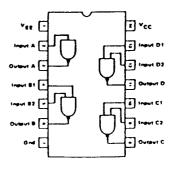

| □ DG271    | page 47 | à | page 48 |

|            | page 49 | à | page 55 |

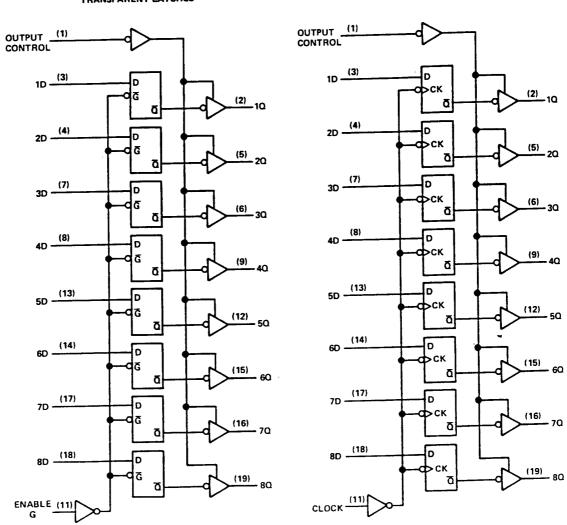

| 74LS374    | page 56 | à | page 57 |

|            | page 58 |   |         |

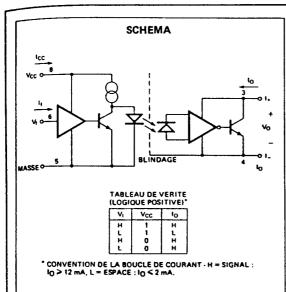

| ☐ HPCL4100 | page 59 | à | page 60 |

| THPCL4200  | page 61 | à | page 62 |

|            | page 63 | à | page 69 |

|            | page 70 | à | page 72 |

# OP-20 MICROPOWER OPERATIONAL AMPLIFIER (SINGLE OR DUAL SUPPLY)

## Precision Monolithics Inc.

#### **FEATURES**

| • | Low Supply Current             | 55µA Max           |

|---|--------------------------------|--------------------|

| • | Single-Supply Operation        | +5V to +30V        |

| • | Dual-Supply Operation          | ±2.5V to ±15V      |

| • | Low Input Offset Voltage       | 250uV Max          |

| • | Low Input Offset Voitage Drift | 1.5 uV/° C Max     |

| • | High Common-Mode Input Range   | . V- to V+ (-1.5V) |

| • | High CMRR and PSRR             | 100dB Min          |

| • | High Open-Loop Gain            | 120dB Min          |

No External Components Required

• 741 Pinout and Nulling

#### **ORDERING INFORMATION**†

|                                                      |                | PACKAGE                  |                         |                                   |

|------------------------------------------------------|----------------|--------------------------|-------------------------|-----------------------------------|

| T <sub>A</sub> = 25°C<br>V <sub>OS</sub> MAX<br>(μV) | TO-99<br>8-PIN | HERMETIC<br>DIP<br>8-PIN | PLASTIC<br>DIP<br>8-PIN | OPERATING<br>TEMPERATURE<br>RANGE |

| 250                                                  | OP20BJ*        | OP20BZ*                  |                         | MIL                               |

| 250                                                  | OP20FJ         | OP20FZ                   |                         | IND                               |

| 250                                                  |                |                          | OP20FP                  | COM                               |

| 500                                                  | OP20CJ*        | OP20CZ*                  |                         | MIL                               |

| 500                                                  | OP20GJ         | OP20GZ                   |                         | IND                               |

| 500                                                  |                |                          | OP20GP                  | COM                               |

| 1000                                                 | OP20HJ         | OP20HZ                   | OP20HP                  | COM                               |

<sup>\*</sup>For devices processed in total compliance to MIL-STD-883, add /883 after part number. Consult factory for 883 data sheet.

#### **GENERAL DESCRIPTION**

The OP-20 is a monolithic micropower operational amplifier that can be operated from a single power supply of  $\pm 50$  to

$\pm 30$ V, or from dual supplies of  $\pm 2.5$ V to  $\pm 15$ V. The input voltage range extends to the negative rail, therefore input signals down to zero volts can be accomodated when operating from a single supply.

Precision performance in high-gain applications is readily obtained when using the OP-20. The B/F grade features a maximum input offset voltage of 250 µV, minimum CMRR of 95dB, and open-loop gain of over 500,000. Quiescent supply current is a maximum of only 55 µA at ±2.5V or 80 µA at ±15V. The low input offset, high gain, and low power consumption brings precision performance to portable instruments, satellites, missile control systems, and many other battery-powered applications.

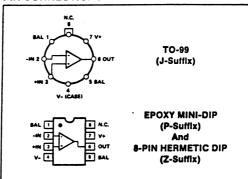

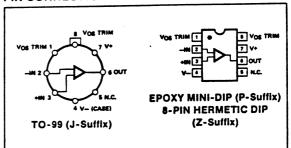

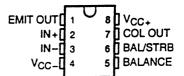

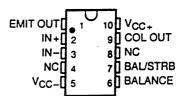

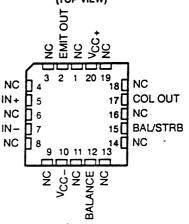

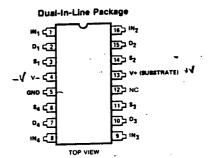

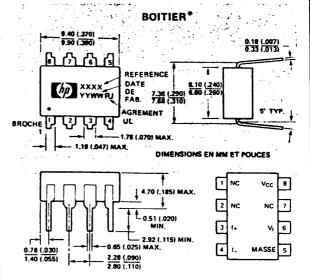

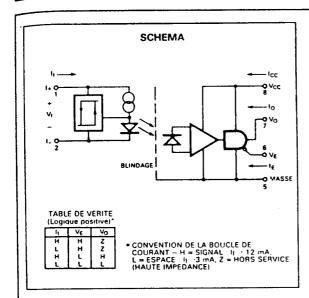

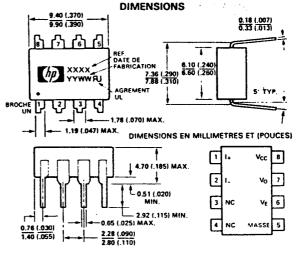

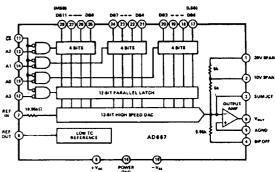

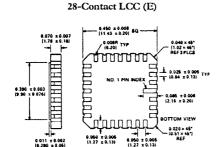

#### **PIN CONNECTIONS**

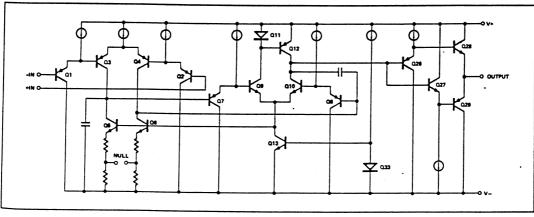

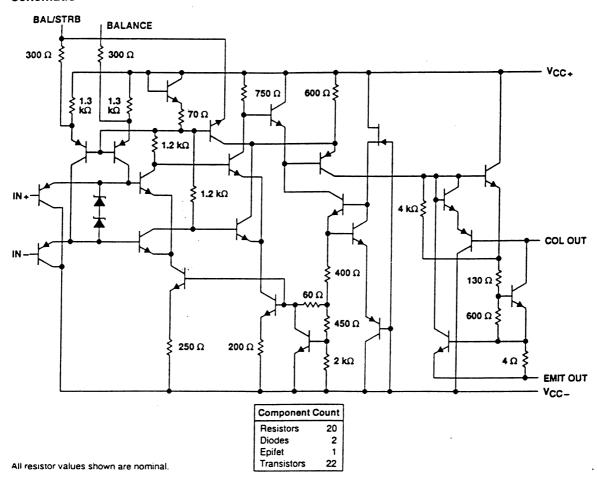

#### SIMPLIFIED SCHEMATIC

part numer: accessors recovery for loss series.

All commercial and industrial temperature range parts are evallable with burn-in. For ordering information see 1986 Data Book, Section 2.

## -PMI

## OP-20 MICROPOWER OPERATIONAL AMPLIFIER

#### **ABSOLUTE MAXIMUM RATINGS (Note 1)**

| Supply Voltage                | ±18V            |

|-------------------------------|-----------------|

| Power Dissipation             | 500mW           |

| Differential Input Voltage    | ±30V            |

| Input Voltage                 |                 |

| Output Short-Circuit Duration | Indefinite      |

| Storage Temperature Range     | •               |

| J and Z Packages              | -65°C to +150°C |

| P Package                     | -65°C to +125°C |

## **ELECTRICAL CHARACTERISTICS** at $V_S = \pm 2.5 V$ to $\pm 15 V$ , $T_A = +25 ^{\circ} C$ , unless otherwise noted.

|                                 |                | C                                                                | P-20B    | /F   | OP-20C/G |          |                | OP-20H     |          |      |      |              |

|---------------------------------|----------------|------------------------------------------------------------------|----------|------|----------|----------|----------------|------------|----------|------|------|--------------|

| PARAMETER                       | SYMBOL         | CONDITIONS                                                       | MIN      | TYP  | MAX      | MIN      | TYP            | MAX        | MIN      | TYP  | MAX  | UNITS        |

| Input Offset Voltage            | Vos            | V <sub>S</sub> = ±15V                                            | _        | 55   | 250      | _        | 150            | 500        | _        | 300  | 1000 | ۷۵           |

| Input Offset Current            | los            | V <sub>CM</sub> = 0                                              |          | 0.15 | 1.5      | -        | 0.2            | 2.5        | _        | 0.3  | 4.0  | nA           |

| Input Bias Current              | I <sub>B</sub> | V <sub>CM</sub> = 0                                              | _        | 12   | 25       | _        | 14             | 30         | _        | 16   | 40   | nA           |

| Input Voltage Range             | IVR            | V+ = +5V,<br>V- = 0V                                             | 0/3.5    | _    | _        | 0/3.5    | -              | _          | 0/3.5    | -    | _    | · v          |

|                                 |                | V <sub>S</sub> = ± 15V                                           | -15/13.5 |      |          | -15/13.5 |                |            | -15/13.5 |      |      |              |

| Common-Mode                     | CMRR           | V+ = +5V, V- = 0V<br>$0V \le V_{CM} \le 3.5V$                    | 95       | 105  | -        | 90       | 95             | -          | 85       | 90   | -    | dB           |

| Rejection Ratio                 |                | V <sub>8</sub> = ±15V<br>-15V ≤ V <sub>CM</sub> ≤ 13.5V          | 100      | 110  | _        | 94       | 105            | _          | 90       | 100  | _    |              |

| Power Supply<br>Rejection Ratio | PSRR           | V <sub>S</sub> = ±2.5V to ±15V<br>and V- = 0V,<br>V+ = 5V to 30V | -        | 4    | 6        | _        | 6              | 10         | -        | 10   | 32   | <b>≱</b> V/∨ |

| Large-Signal                    |                | V+ = +5V, V- = 0V<br>1V ≤ V <sub>O</sub> ≤ 3.5V                  | 300      | 500  | -        | 200      | 500            | _          | _        | 500  | -    | V/mV         |

| Voltage Gain                    | <b>^v</b> o    | $V_S = \pm 15V$ , $V_O = \pm 10V$<br>$R_L = 25k\Omega$           | 1000     | 2000 | -        | 800      | 2000           | <b>-</b> . | 500      | 1000 | -    | •////        |

|                                 |                | V+ = 5V, V- = 0V                                                 | 0.6/4.1  | _    | -        | 0.7/4.1  | -              | -          | 0.8/4.0  | _    | -    |              |

| Output Voltage<br>Swing         | V <sub>O</sub> | $R_L = 10k\Omega$<br>$V_S = \pm 15V$ ,<br>$R_L = 25k\Omega$      | ±14.1    | _    | -        | ±14.1    | , <del>-</del> | -          | ±14.0    | -    | -    | <b>v</b>     |

| Closed-Loop<br>Bandwidth        | BW             | A <sub>VCL</sub> = +1.0,<br>R <sub>L</sub> = 10kΩ                | -        | 100  | _        | -        | 100            | _          | -        | 100  | _    | kHz          |

| Slew Rate                       | SA             | $V_S = \pm 15V$<br>$R_L = 25k\Omega$                             | _        | 0.05 | -        | -        | 0.05           | -          | -        | 0.05 | -    | <b>۷/μ</b> 8 |

| Supply Current                  | 1.             | V <sub>S</sub> = ±2.5V,<br>No Load                               |          | 40   | 55       | _        | 44             | 63         |          | 45   | 70   | ٨٨           |

| Supply Content                  | İsy            | V <sub>S</sub> = ±15V,<br>No Load                                | -        | 55   | 80       | _        | 57             | 85         |          | 60   | 95   |              |

Absolute ratings apply to both DICE and packaged parts, unless otherwise noted.

# Low Cost, Miniature Isolation Amplifiers

# AD202/AD204

#### **FEATURES**

Small Size: 4 Channels/Inch Low Power: 35 mW (AD204)

High Accuracy: ±0.025% max Nonlinearity (K Grade)

High CMR: 130 dB (Gain = 100 V/V)

Wide Bandwidth: 5 kHz Full-Power (AD204)

High CMV Isolation: ±2000 V pk Continuous (K Grade)

(Signal and Power)

Isolated Power Outputs

Uncommitted Input Amplifier

**APPLICATIONS**

Multichannel Data Acquisition Current Shunt Measurements Motor Controls Process Signal Isolation High Voltage Instrumentation Amplifier

#### **GENERAL DESCRIPTION**

The AD202 and AD204 are general purpose, two-port, transformer-coupled isolation amplifiers that may be used in a broad range of applications where input signals must be measured, processed and/or transmitted without a galvanic connection. These industry standard isolation amplifiers offer a complete isolation function, with both signal and power isolation provided for in a single compact plastic SIP or DIP style package. The primary distinction between the AD202 and the AD204 is that the AD202 is powered directly from a +15 V dc supply while the AD204 is powered by an externally supplied clock, such as the recommended AD246 Clock Driver.

The AD202 and AD204 provide total galvanic isolation between the input and output stages of the isolation amplifier through the use of internal transformer-coupling. The functionally complete AD202 and AD204 eliminate the need for an external, user-supplied dc/dc converter. This permits the designer to minimize the necessary circuit overhead and consequently reduce the overall design and component costs.

The design of the AD202 and AD204 emphasizes maximum flexibility and ease of use, including the availability of an uncommitted op amp on the input stage. They feature a bipolar ±5 V output range, an adjustable gain range of from 1 to 100 V/V, ±0.025% max nonlinearity (K grade), 130 dB of CMR and the AD204 consumes a low 35 mW of power.

#### PRODUCT HIGHLIGHTS

The AD202 and AD204 are full-featured isolators offering numerous benefits to the user:

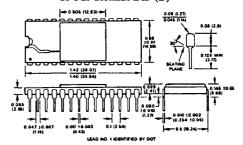

**Small Size:** The AD202 and AD204 are available in SIP and DIP form packages. The SIP package is just 0.25" wide, giving the user a channel density of four channels per inch. The isolation barrier is positioned to maximize input to output spac-REV. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

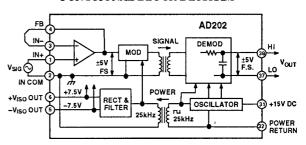

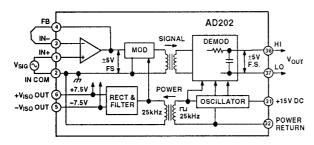

#### FUNCTIONAL BLOCK DIAGRAM

ing. For applications requiring a low profile, the DIP package provides a height of just 0.350".

High Accuracy: With a maximum nonlinearity of ±0.025% for the AD202K/AD204K (±0.05% for the AD202J/AD204J) and low drift over temperature, the AD202 and AD204 provide high isolation without loss of signal integrity.

Low Power: Power consumption of 35 mW (AD204) and 75 mW (AD202) over the full signal range makes these isolators ideal for use in applications with large channel counts or tight power budgets.

Wide Bandwidth: The AD204's full-power bandwidth of 5 kHz makes it useful for wideband signals. It is also effective in applications like control loops, where limited bandwidth could result in instability.

Excellent Common-Mode Performance: The AD202K/ AD204K provide  $\pm 2000$  V pk continuous common-mode isolation, while the AD202J/AD204J provide  $\pm 1000$  V pk continuous common-mode isolation. All models have a total common-mode input capacitance of less than 5 pF inclusive of power isolation. This results in CMR ranging from 130 dB at a gain of 100 dB to 104 dB (minimum at unity gain) and very low leakage current (2  $\mu$ A maximum).

Flexible Input: An uncommitted op amp is provided at the input of all models. This provides buffering and gain as required, and facilitates many alternative input functions including filtering, summing, high-voltage ranges, and current (transimpedance) input.

Isolated Power: The AD204 can supply isolated power of  $\pm 7.5~V$  at 2 mA. This is sufficient to operate a low-drift input preamp, provide excitation to a semiconductor strain gage, or to power any of a wide range of user-supplied ancillary circuits. The AD202 can supply  $\pm 7.5~V$  at 0.4 mA which is sufficient to operate adjustment networks or low-power references and op amps, or to provide an open-input alarm.

O Analog Devices, Inc., 1994

One Technology Way, P.O. Box 9106, Norwood. MA 02062-9106, U.S.A. Tel: 617/329-4700 Fax: 617/326-8703

# AD202/AD204—SPECIFICATIONS (typical @ + 25°C & V<sub>s</sub> = +15 V unless otherwise noted)

| Model                                                                                 | AD204J                                             | AD204K                            | AD202J                    | AD202K        |

|---------------------------------------------------------------------------------------|----------------------------------------------------|-----------------------------------|---------------------------|---------------|

| GAIN                                                                                  |                                                    |                                   |                           |               |

| Range                                                                                 | 1 V/V-100 V/V                                      | *                                 | *                         | *             |

| Error                                                                                 | ±0.5% typ (±4% max)                                | *                                 | *                         | *             |

| vs. Temperature                                                                       | ±20 ppm/°C typ (±45 ppm/°C max)                    | <u> </u> *                        | *                         | *             |

| vs. Time                                                                              | ±50 ppm/1000 Hours                                 | *                                 | *                         | *             |

| vs. Supply Voltage                                                                    | ±0.01%/V                                           | ±0.01%/V                          | ±0.01%/V                  | ±0.01%/V      |

| Nonlinearity $(G = 1 \text{ V/V})^1$                                                  | ±0.05% max                                         | ±0.025% max                       | ±0.05% max                | ±0.025% max   |

| Nonlinearity vs. Isolated Supply Load                                                 | ±0.0015%/mA                                        | * 10.025 /6 Illax                 | *                         | *             |

|                                                                                       | ±0.0013 /6/IIIA                                    | <u> </u>                          |                           |               |

| INPUT VOLTAGE RATINGS                                                                 |                                                    | *                                 | *                         | *             |

| Input Voltage Range                                                                   | ±5 V                                               | 1^                                | Î.                        | ^             |

| Max Isolation Voltage (Input to Output)                                               |                                                    | 1                                 |                           |               |

| AC, 60 Hz, Continuous                                                                 | 750 V rms                                          | 1500 V rms                        | 750 V rms                 | 1500 V rms    |

| Continuous (AC and DC)                                                                | ± 1000 V Peak                                      | ±2000 V Peak                      | ±1000 V Peak              | ±2000 V Peak  |

| Isolation-Mode Rejection Ratio (IMRR) @ 60 Hz                                         |                                                    |                                   |                           |               |

| $R_S \le 100 \Omega$ (HI & LO Inputs) $G = 1 \text{ V/V}$                             | 110 dB                                             | 110 dB                            | 105 dB                    | 105 dB        |

| G = 100  V/V                                                                          | 130 dB                                             | *                                 | *                         | *             |

| $R_S \le 1 k\Omega$ (Input HI, LO, or Both) $G = 1 \text{ V/V}$                       | 104 dB min                                         | 104 dB min                        | 100 dB min                | 100 dB min    |

| G = 100  V/V                                                                          | 110 dB min                                         | *                                 | *                         | *             |

| Leakage Current Input to Output @ (240 V rms, 60 Hz                                   |                                                    | *                                 | *                         | *¹            |

|                                                                                       | 2 justinis max                                     |                                   |                           |               |

| INPUT IMPEDANCE                                                                       |                                                    | 1                                 |                           |               |

| Differential ( $G = 1 \text{ V/V}$ )                                                  | $10^{12} \Omega$                                   | *                                 | *                         | *             |

| Common Mode                                                                           | 2 GΩ 4.5 pF                                        | *                                 | *                         | *             |

| INPUT BIAS CURRENT                                                                    |                                                    |                                   |                           |               |

|                                                                                       | ±30 pA                                             | *                                 | *                         | *             |

| Initial, @ +25°C                                                                      | ± 10 nA                                            | 1*                                | *                         | *             |

| vs. Temperature (0°C to +70°C)                                                        | ± 10 nA                                            | ļ                                 |                           |               |

| INPUT DIFFERENCE CURRENT                                                              | i                                                  |                                   |                           |               |

| Initial, @ +25°C                                                                      | ±5 pA                                              | *                                 | *                         | *             |

| vs. Temperature (0°C to +70°C)                                                        | ±2 nA                                              | *                                 | *                         | *             |

| INPUT NOISE                                                                           |                                                    |                                   |                           |               |

|                                                                                       | 4.37                                               | l.                                | *                         | *             |

| Voltage, 0.1 Hz to 100 Hz                                                             | 4 μV p-p                                           |                                   | *                         | ,<br>*        |

| f > 200 Hz                                                                            | 50 nV/√Hz                                          | *                                 | ×                         | ×             |

| FREQUENCY RESPONSE                                                                    |                                                    | 1                                 |                           |               |

| Bandwidth ( $V_0 \le 10 \text{ V p-p}$ , $G = 1 \text{ V}-50 \text{ V/V}$ )           | 5 kHz                                              | 5 kHz                             | 2 kHz                     | 2 kHz         |

| Settling Time, to ±10 mV (10 V Step)                                                  | 1 ms                                               | *                                 | *                         | *             |

|                                                                                       | 1 1115                                             |                                   |                           |               |

| OFFSET VOLTAGE (RTI)                                                                  |                                                    | 1                                 |                           |               |

| Initial, @ +25°C Adjustable to Zero                                                   | (±15 ±15/G)mV max                                  | $(\pm 5 \pm 5/G)$ mVmax           | $(\pm 15 \pm 15/G)$ mVmax | (±5 ±5/G)mVma |

|                                                                                       | ( 10)                                              | 1                                 |                           |               |

| vs . Temperature (0°C to +70°C)                                                       | $\left( \pm 10 \pm \frac{10}{G} \right) \mu V / C$ |                                   | ļ                         |               |

| vs. Temperature (0 C to 110 C)                                                        | $(G)^{\circ}$                                      |                                   |                           |               |

| DATED ALTERIA                                                                         |                                                    |                                   |                           |               |

| RATED OUTPUT                                                                          | l                                                  | 1.                                |                           |               |

| Voltage (Out HI to Out LO)                                                            | ±5 V                                               | *                                 | *                         | *             |

| Voltage at Out HI or Out LO (Ref. Pin 32)                                             | ±6.5 V                                             | *                                 | *                         | *             |

| Output Resistance                                                                     | 3 kΩ                                               | 3 kΩ                              | 7 kΩ                      | 7 kΩ          |

| Output Ripple, 100 kHz Bandwidth                                                      | 10 mV pk-pk                                        | *                                 | *                         | *             |

| 5 kHz Bandwidth                                                                       | 0.5 mV rms                                         | *                                 | *                         | *             |

| IGOLATED DOWED OF THE STATE                                                           |                                                    |                                   |                           |               |

| ISOLATED POWER OUTPUT <sup>2</sup>                                                    | 1.253                                              | 1.                                | 1.                        | *             |

| Voltage, No Load                                                                      | ±7.5 V                                             | 11                                | 1                         | 11            |

| Accuracy                                                                              | ±10%                                               | T                                 | ×                         | l * .         |

| Current                                                                               | 2 mA (Either Output) <sup>3</sup>                  | 2 mA (Either Output) <sup>3</sup> | 400 μA Total              | 400 μA Total  |

| Regulation, No Load to Full Load                                                      | 5%                                                 | *                                 | *                         | *             |

| Ripple                                                                                | 100 mV pk-pk                                       | *                                 | *                         | *             |

| OSCILLATOR DRIVE INPUT                                                                |                                                    |                                   |                           |               |

|                                                                                       | LE Valent Nemi 1                                   | 15 V -11- N                       | lava.                     | NT/A          |

| Input Voltage                                                                         | 15 V pk-pk Nominal                                 | 15 V pk-pk Nominal                | N/A                       | N/A           |

| Input Frequency                                                                       | 25 kHz Nominal                                     | 25 kHz Nominal                    | N/A                       | N/A           |

| POWER SUPPLY (AD202 Only)                                                             |                                                    |                                   |                           |               |

| Voltage, Rated Performance                                                            | N/A                                                | N/A                               | +15 V ± 5%                | +15 V ± 5%    |

| Voltage, Operating                                                                    | N/A                                                | N/A                               | +15 V ± 10%               | +15 V ± 10%   |

|                                                                                       | N/A                                                | N/A                               | 5 mA                      | 5 mA          |

| Current No Load (Vo = +15 V)                                                          |                                                    |                                   |                           |               |

| Current, No Load (V <sub>S</sub> = +15 V)                                             |                                                    | 1                                 | l.                        | l .           |

| TEMPERATURE RANGE                                                                     |                                                    |                                   | 1 *                       | *             |

|                                                                                       | 0°C to +70°C                                       | *                                 | <u> </u> ^                |               |

| TEMPERATURE RANGE Rated Performance                                                   | 0°C to +70°C<br>-40°C to +85°C                     | *                                 | *                         | *             |

| TEMPERATURE RANGE Rated Performance Operating                                         |                                                    |                                   | ^<br> *<br> *             | *             |

| TEMPERATURE RANGE<br>Rated Performance<br>Operating<br>Storage                        | -40°C to +85°C                                     | *                                 |                           | 1             |

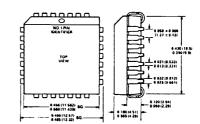

| TEMPERATURE RANGE Rated Performance Operating Storage PACKAGE DIMENSIONS <sup>4</sup> | -40°C to +85°C<br>-40°C to +85°C                   | * *                               | *                         | *             |

| TEMPERATURE RANGE Rated Performance Operating Storage                                 | -40°C to +85°C                                     | *                                 |                           | 1             |

NOTES

Specifications same as AD204].

Nonlinearity is specified as a % deviation from a best straight line.

1.0 µF min decoupling required (see text).

3 mA with one supply loaded.

4Width is 0.25" typ, 0.26" max.

Specifications subject to change without notice.

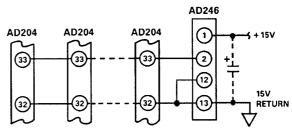

#### **DIFFERENCES BETWEEN THE AD202 AND AD204**

The primary distinction between the AD202 and AD204 is in the method by which they are powered: the AD202 operates directly from +15 V dc while the AD204 is powered by a non-isolated externally-supplied clock (AD246) which can drive up to 32 AD204s. The main advantages of using the externally-clocked AD204 over the AD202 are reduced cost in multichannel applications, lower power consumption, and higher bandwidth. In addition, the AD204 can supply substantially more isolated power than the AD202.

Of course, in a great many situations, especially where only one or a few isolators are used, the convenience of stand-alone operation provided by the AD202 will be more significant than any of the AD204's advantages. There may also be cases where it is desirable to accommodate either device interchangeably, so the pinouts of the two products have been designed to make that easy to do.

Figure 1a. AD202 Functional Block Diagram

Figure 1b. AD204 Functional Block Diagram (Pin Designations Apply to the DIP-Style Package)

#### **INSIDE THE AD202 AND AD204**

The AD202 and AD204 use an amplitude modulation technique to permit transformer coupling of signals down to dc (Figure 1a and 1b). Both models also contain an uncommitted input op amp and a power transformer which provides isolated power to the op amp, the modulator, and any external load. The power transformer primary is driven by a 25 kHz, 15 V p-p square wave which is generated internally in the case of the AD202, or supplied externally for the AD204.

Within the signal swing limits of approximately ±5 V, the output voltage of the isolator is equal to the output voltage of the op amp; that is, the isolation barrier has unity gain. The output signal is not internally buffered, so the user is free to interchange the output leads to get signal inversion. Additionally, in multichannel applications, the unbuffered outputs can be multiplexed with one buffer following the mux. This technique minimizes offset errors while reducing power consumption and cost. The

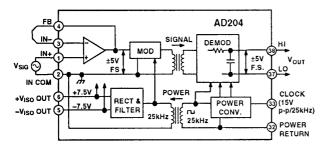

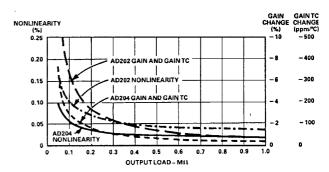

output resistance of the isolator is typically 3 k $\Omega$  for the AD204 (7 k $\Omega$  for AD202) and varies with signal level and temperature, so it should not be loaded (see Figure 2 for the effects of load upon nonlinearity and gain drift). In many cases a high-impedance load will be present or a following circuit such as an output filter can serve as a buffer, so that a separate buffer function will not often be needed.

Figure 2. Effects of Output Loading

## USING THE AD202 AND AD204

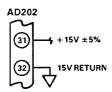

Powering the AD202. The AD202 requires only a single +15 V power supply connected as shown in Figure 3a. A bypass capacitor is provided in the module.

Figure 3a.

Powering the AD204. The AD204 gets its power from an externally supplied clock signal (a 15 V p-p square wave with a nominal frequency of 25 kHz) as shown in Figure 3b.

Figure 3b.

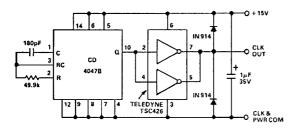

AD246 Clock Driver. The AD246 is a compact, inexpensive clock driver that can be used to obtain the required clock from a single 15 V supply. Alternatively, the circuit shown in Figure 4 (essentially an AD246) can be used. In either case, one clock circuit can operate at least 32 AD204s at the rated minimum supply voltage of 14.25 V and one additional isolator can be operated for each 40 mV increase in supply voltage up to 15 V. A supply bypass capacitor is included in the AD246, but if many

(Circuit figures shown on this page are for SIP style packages. Refer to page 3 for proper DIP package pinout.)

AD204s are operated from a single AD246, an external bypass capacitor should be used with a value of at least 1  $\mu$ F for every five isolators used. Place the capacitor as close as possible to the clock driver.

Figure 4. Clock Driver

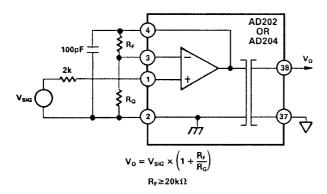

Input Configurations. The AD202 and AD204 have been designed to be very easy to use in a wide range of applications. The basic connection for standard unity gain applications, useful for signals up to ±5 V, is shown in Figure 5; some of the possible variations are described below. When smaller signals must be

Figure 5. Basic Unity-Gain Application

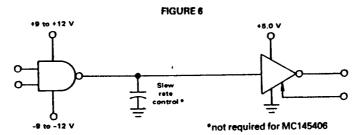

handled, Figure 6 shows how to get gain while preserving a very high input resistance. The value of feedback resistor  $R_F$  should be kept above 20  $k\Omega$  for best results. Whenever a gain of more than five is taken, a 100 pF capacitor from FB to IN COM is required. At lower gains this capacitor is unnecessary, but it will not adversely affect performance if used.

Figure 6. Input Connections for Gain > 1

The "noninverting" circuit of Figures 5 and 6 can also be used to advantage when a signal inversion is needed: just interchange either the input leads or the output leads to get inversion. This approach retains the high input resistance of the "noninverting" circuit, and at unity gain no gain-setting resistors are needed.

When the isolator is not powered, a negative input voltage of more than about 2 V will cause an input current to flow. If the signal source can supply more than a few mA under such conditions, the 2 k $\Omega$  resistor shown in series with IN+ should be used to limit current to a safe value. This is particularly important with the AD202, which may not start if a large input current is present.

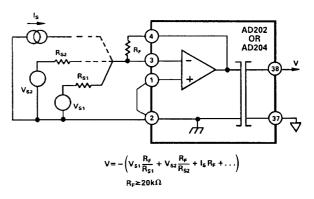

Figure 7 shows how to accommodate current inputs or sum currents or voltages. This circuit can also be used when the input signal is larger than the  $\pm 5$  V input range of the isolator; for example, a  $\pm 50$  V input span can be accommodated with  $R_F$  = 20 k and  $R_S$  = 200 k. Once again, a capacitor from FB to IN COM is required for gains above five.

Figure 7. Connections for Summing or Current Inputs

Adjustments. When gain and zero adjustments are needed, the circuit details will depend on whether adjustments are to be made at the isolator input or output, and (for input adjustments) on the input circuit used. Adjustments are usually best done on the input side, because it is better to null the zero ahead of the gain, and because gain adjustment is most easily done as part of the gain-setting network. Input adjustments are also to be preferred when the pots will be near the input end of the isolator (to minimize common-mode strays). Adjustments on the output side might be used if pots on the input side would represent a hazard due to the presence of large common-mode voltages during adjustment.

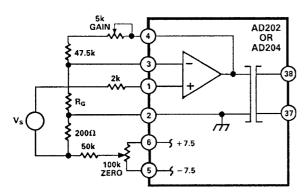

Figure 8a shows the input-side adjustment connections for use with the "noninverting" connection of the input amplifier. The zero adjustment circuit injects a small adjustment voltage in series with the low side of the signal source. (This will not work if the source has another current path to input common or if current flows in the signal source LO lead). Since the adjustment voltage is injected ahead of the gain, the values shown will

(Circuit figures shown on this page are for SIP style packages. Refer to Page 3 for proper DIP package pinout.)

חביי ה

work for any gain. Keep the resistance in series with input LO below a few hundred ohms to avoid CMR degradation.

Figure 8a. Adjustments for Noninverting Connection of Op Amp

Also shown in Figure 8a is the preferred means of adjusting the gain-setting network. The circuit shown gives a nominal  $R_F$  of 50 k $\Omega$ , and will work properly for gains of ten or greater. The adjustment becomes less effective at lower gains (its effect is halved at G=2) so that the pot will have to be a larger fraction of the total  $R_F$  at low gain. At G=1 (follower) the gain cannot be adjusted downward without compromising input resistance; it is better to adjust gain at the signal source or after the output.

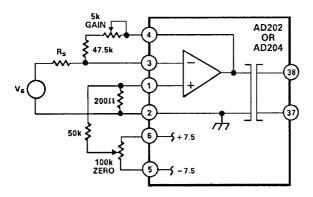

Figure 8b shows adjustments for use with inverting input circuits. The zero adjustment nulls the voltage at the summing node. This method is preferable to current injection because it is less affected by subsequent gain adjustment. Gain adjustment is again done in the feedback; but in this case it will work all the way down to unity gain (and below) without alteration.

Figure 8b. Adjustments for Summing or Current Input

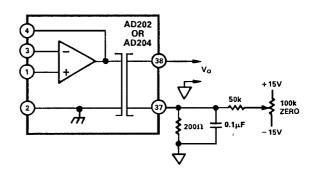

Figure 9 shows how zero adjustment is done at the output by taking advantage of the semi-floating output port. The range of this adjustment will have to be increased at higher gains; if that is done, be sure to use a suitably stable supply voltage for the pot circuit.

There is no easy way to adjust gain at the output side of the isolator itself. If gain adjustment must be done on the output side, it will have to be in a following circuit such as an output buffer or filter.

Figure 9. Output-Side Zero Adjustment

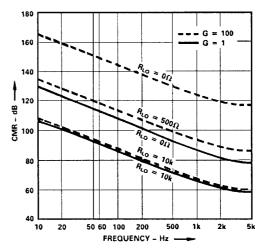

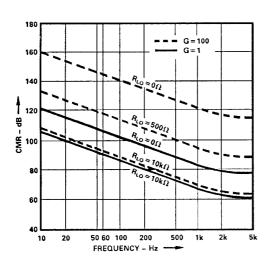

Common-Mode Performance. Figures 10a and 10b show how the common-mode rejection of the AD202 and AD204 varies with frequency, gain, and source resistance. For these isolators, the significant resistance will normally be that the path from the source of the common-mode signal to IN COM. The AD202 and AD204 also perform well in applications requiring rejection of fast common-mode steps, as described in the Applications section.

Figure 10a. AD204

(Circuit figures shown on this page are for SIP style packages. Refer to page 3 for proper DIP package pinout.)

Figure 10b. AD202

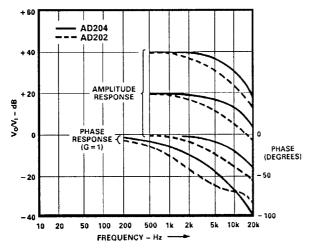

Dynamics and Noise. Frequency response plots for the AD202 and AD204 are given in Figure 11. Since neither isolator is slew-rate limited, the plots apply for both large and small signals. Capacitive loads of up to 470 pF will not materially affect frequency response. When large signals beyond a few hundred Hz will be present, it is advisable to bypass -V $_{\rm ISO}$  and +V $_{\rm ISO}$  to IN COM with 1  $\mu\rm F$  tantalum capacitors even if the isolated supplies are not loaded.

At 50 Hz/60 Hz, phase shift through the AD202/AD204 is typically 0.8° (lagging). Typical unit—unit variation is  $\pm 0.2^{\circ}$  (lagging).

Figure 11. Frequency Response at Several Gains

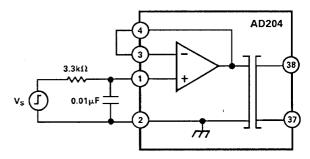

The step response of the AD204 for very fast input signals can be improved by the use of an input filter, as shown in Figure 12. The filter limits the bandwidth of the input (to about 5.3 kHz) so that the isolator does not see fast, out-of-band input terms that can cause small amounts ( $\pm 0.3\%$ ) of internal ringing. The AD204 will then settle to  $\pm 0.1\%$  in about 300 microseconds for a 10 V step.

Figure 12. Input Filter for Improved Step Response

Except at the highest useful gains, the noise seen at the output of the AD202 and AD204 will be almost entirely comprised of carrier ripple at multiples of 25 kHz. The ripple is typically 2 mV p-p near zero output and increases to about 7 mV p-p for outputs of  $\pm 5$  V (1 MHz measurement bandwidth). Adding a capacitor across the output will reduce ripple at the expense of bandwidth: for example, 0.05  $\mu$ F at the output of the AD204 will result in 1.5 mV ripple at  $\pm 5$  V, but signal bandwidth will be down to 1 kHz.

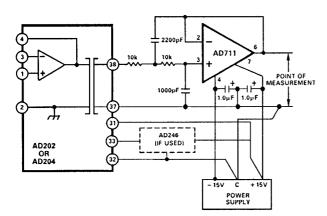

When the full isolator bandwidth is needed, the simple two-pole active filter shown in Figure 13 can be used. It will reduce ripple to 0.1 mV p-p with no loss of signal bandwidth, and also serves as an output buffer.

An output buffer or filter may sometimes show output spikes that do not appear at its input. This is usually due to clock noise appearing at the op amp's supply pins (since most op amps have little or no supply rejection at high frequencies). Another common source of carrier-related noise is the sharing of a ground track by both the output circuit and the power input. Figure 13 shows how to avoid these problems: the clock/supply port of the isolator does not share ground or 15 V tracks with any signal circuits, and the op amp's supply pins are bypassed to signal common (note that the grounded filter capacitor goes here as well). Ideally, the output signal LO lead and the supply common meet where the isolator output is actually measured, e.g., at an A/D converter input. If that point is more than a few feet from the isolator, it may be useful to bypass output LO to supply common at the isolator with a 0.1 µF capacitor.

In applications where more than a few AD204s are driven by a single clock driver, substantial current spikes will flow in the power return line and in whichever signal out lead returns to a low impedance point (usually output LO). Both of these tracks

(Circuit figures shown on this page are for SIP style packages. Refer to page 3 for proper DIP package pinout.)

should be made large to minimize inductance and resistance; ideally, output LO should be directly connected to a ground plane which serves as measurement common.

Current spikes can be greatly reduced by connecting a small inductance (68  $\mu$ H-100  $\mu$ H) in series with the clock pin of each AD204. Molded chokes such as the Dale IM-2 series, with dc resistance of about 5  $\Omega$ , are suitable.

Figure 13. Output Filter Circuit Showing Proper Grounding

Using Isolated Power. Both the AD202 and the AD204 provide ±7.5 V power outputs referenced to input common. These may be used to power various accessory circuits which must operate at the input common-mode level; the input zero adjustment pots described above are an example, and several other possible uses are shown in the section titled Application Examples.

The isolated power output of the AD202 ( $400 \, \mu A$  total from either or both outputs) is much more limited in current capacity than that of the AD204, but it is sufficient for operating micropower op amps, low power references (such as the AD589), adjustment circuits, and the like.

The AD204 gets its power from an external clock driver, and can handle loads on its isolated supply outputs of 2 mA for each supply terminal (+7.5 V and -7.5 V) or 3 mA for a single loaded output. Whenever the external load on either supply is more than about 200  $\mu$ A, a 1  $\mu$ F tantalum capacitor should be used to bypass each loaded supply pin to input common.

Up to 32 AD204s can be driven from a single AD246 (or equivalent) clock driver when the isolated power outputs of the AD204s are loaded with less than 200  $\mu A$  each, at a worst-case supply voltage of 14.25 V at the clock driver. The number of AD204s that can be driven by one clock driver is reduced by one AD204 per 3.5 mA of isolated power load current at 7.5 V, distributed in any way over the AD204s being supplied by that clock driver. Thus a load of 1.75 mA from +V $_{\rm ISO}$  to -V $_{\rm ISO}$  would also count as one isolator because it spans 15 V.

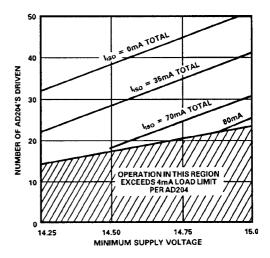

It is possible to increase clock fanout by increasing supply voltage above the 14.25 V minimum required for 32 loads. One additional isolator (or 3.5 mA unit load) can be driven for each 40 mV of increase in supply voltage up to 15 V. Therefore if the minimum supply voltage can be held to 15 V – 1%, it is possible to operate 32 AD204s and 52 mA of 7.5 V loads. Figure 14 shows the allowable combinations of load current and channel count for various supply voltages.

Figure 14. AD246 Fanout Rules

Synchronization. Since AD204s operate from a common clock, synchronization is inherent. AD202s will normally not interact to produce beat frequencies even when mounted on 0.25-inch centers. Interaction may occur in rare situations where a large number of long, unshielded input cables are bundled together and channel gains are high. In such cases, shielded cable may be required or AD204s can be used.

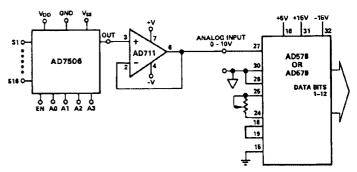

#### APPLICATIONS EXAMPLES

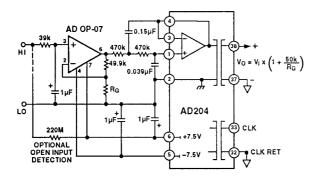

Low-Level Sensor Inputs. In applications where the output of low-level sensors such as thermocouples must be isolated, a low drift input amplifier can be used with an AD204, as shown in Figure 17. A three-pole active filter is included in the design to get normal-mode rejection of frequencies above a few Hz and to provide enhanced common-mode rejection at 60 Hz. If offset adjustment is needed, it is best done at the trim pins of the OP07 itself; gain adjustment can be done at the feedback resistor.

Figure 17. Input Amplifier & Filter for Sensor Signals

Note that the isolated supply current is large enough to mandate the use of 1  $\mu$ F supply bypass capacitors. This circuit can be used with an AD202 if a low-power op amp is used instead of the OP07.

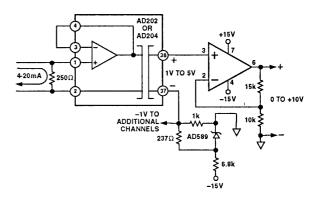

Process Current Input with Offset. Figure 18 shows an isolator receiver which translates a 4-20 mA process current signal into a 0 V to +10 V output. A 1 V to 5 V signal appears at the isolator's output, and a -1 V reference applied to output LO provides the necessary level shift (in multichannel applications, the reference can be shared by all channels). This technique is often useful for getting offset with a follower-type output buffer.

Figure 18. Process Current Input Isolator with Offset

The circuit as shown requires a source compliance of at least 5 V, but if necessary that can be reduced by using a lower value of current-sampling resistor and configuring the input amplifier for a small gain.

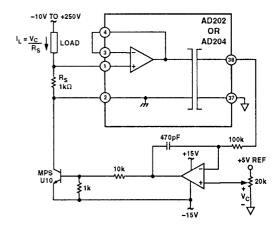

High-Compliance Current Source. In Figure 19, an isolator is used to sense the voltage across current-sensing resistor R to allow direct feedback control of a high-voltage transistor or FET used as a high-compliance current source. Since the isolator has virtually no response to dc common-mode voltage, the closed-loop current source has a static output resistance greater than  $10^{14}\,\Omega$  even for output currents of several mA. The output current capability of the circuit is limited only by power dissipation in the source transistor.

Figure 19. High-Compliance Current Source

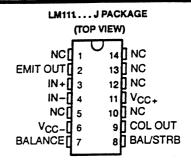

**OP-77**

**NEXT GENERATION OP-07**

(ULTRA-LOW OFFSET VOLTAGE OPERATIONAL AMPLIFIER)

## Precision Monolithics Inc

#### **FEATURES**

| • | Outst | anding | Gain | Linearity |

|---|-------|--------|------|-----------|

|   |       |        |      |           |

| • | Ultra High Gain       | 5000V/mV Min                   |

|---|-----------------------|--------------------------------|

| • | Low Vos               | 25 µV Max                      |

| • | Excellent TCVos       | 0.3µV/°C Max                   |

| • | High PSRR             | 3μV/V Max                      |

| • | High CMRR             | 1.0 <sub>\(\mu\)</sub> V/V Max |

|   | Low Power Consumption |                                |

<sup>•</sup> Fits OP-07, 725, 108A/308A, 741 Sockets

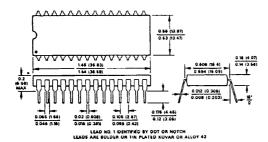

#### ORDERING INFORMATION

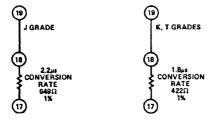

| PACKAGE                  |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HERMETIC<br>DIP<br>8-PIN | PLASTIC<br>DIP<br>8-PIN                                            | OPERATING<br>TEMPERATURE<br>RANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OP77AZ*                  |                                                                    | MIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| OP77EZ                   | OP77EP                                                             | IND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| OP77BZ*                  |                                                                    | MIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| OP77FZ                   | OP77FP                                                             | IND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| OP77GZ                   | OP77GP                                                             | COM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                          | HERMETIC<br>DIP<br>8-PIN<br>OP77AZ'<br>OP77EZ<br>OP77BZ'<br>OP77FZ | HERMETIC   PLASTIC   DIP   8-PIN   8-PIN     0P77AZ'   0P77EZ   0P77EZ   0P77FZ   0P77FZ |

<sup>\*</sup>For devices processed in total compliance to MIL-STD-883, add /883 after part number. Consult factory for 883 data sheet.

#### **GENERAL DESCRIPTION**

The OP-77 significantly advances the state-of-the-art in precision op amps. The OP-77's outstanding gain of 10,000,000 or more is maintained over the full ±10V output range. This exceptional gain-linearity eliminates incorrectable system nonlinearities common in previous monolithic op amps, and provides superior performance in high closed-loop-gain applications.

## PRELIMINARY

Low initial  $V_{OS}$  drift and rapid stabilization time, combined with only 50mW power consumption, are significant improvements over previous designs. These characteristics, plus the exceptional TCV<sub>OS</sub> of  $0.3\mu$ V/°C maximum and the low V<sub>OS</sub> of  $25\mu$ V maximum, eliminates the need for V<sub>OS</sub> adjustment and increases system accuracy over temperature.

PSRR of  $3\mu V/V$  (110dB) and CMRR of  $1.0\mu V/V$  maximum virtually eliminate errors caused by power supply drifts and common-mode signals. This combination of outstanding characteristics makes the OP-77 ideally suited for high-resolution instrumentation and other tight error budget systems.

This product is available in five standard grades and three standard packages: the TO-99 can and the 8-pin mini-dip in ceramic or epoxy.

The OP-77 is a direct or upgrade replacement for the OP-07. OP-05, 725, or 108A op amps. 741-types can be replaced by eliminating the  $V_{OS}$  adjust pot.

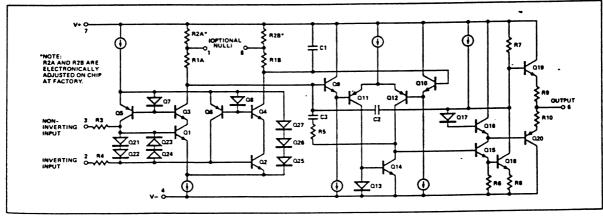

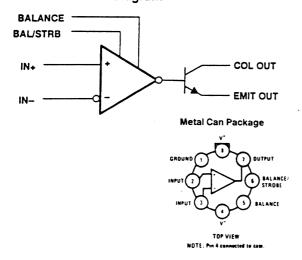

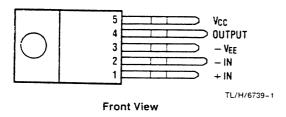

#### PIN CONNECTIONS

#### SIMPLIFIED SCHEMATIC

This preliminary product information is based on testing of a limited number of devices. Final specifications may vary, Please contact local sales office or distributor for final data sheet.

1/86, Rev. A

<sup>†</sup>All commercial and industrial temperature range parts are available with burn-in. For ordering information see 1986 Data Book, Section 2.

## PMI)

#### OP-77 NEXT GENERATION OP-07 — PRELIMINARY

## ABSOLUTE MAXIMUM RATINGS (Note 2)

| Supply Voltage ±22V                                       |

|-----------------------------------------------------------|

| Internal Power Dissipation (Note 1)500mW                  |

| Differential Input Voltage ±30V                           |

| Input Voltage (Note 3) ±22V                               |

| Output Short-Circuit DurationIndefinite                   |

| Storage Temperature Range .                               |

| J and Z Packages65°C to +150°C                            |

| P Package65°C to +125°C                                   |

| Operating Temperature Range                               |

| OP-77A, OP-77B55°C to +125°C                              |

| OP-77E, OP-77F25°C to +85°C                               |

| OP-77G 0°C to 70°C                                        |

| Lead Temperature Range (Soldering, 60 sec)300°C           |

| DICE Junction Temperature (T <sub>1</sub> )65°C to +150°C |

#### NOTES:

1. See table for maximum ambient temperature rating and derating factor.

| PACKAGE TYPE           | MAXIMUM AMBIENT<br>TEMPERATURE<br>FOR RATING | DERATE ABOVE<br>MAXIMUM AMBIEN<br>TEMPERATURE |  |  |

|------------------------|----------------------------------------------|-----------------------------------------------|--|--|

| TO-99 (J)              | 90°C                                         | 7.1mW/°C                                      |  |  |

| 8-Pin Hermetic DIP (Z) | 75°C                                         | 6.7mW/°C                                      |  |  |

| 6-Pin Plastic DIP (P)  | 36°C                                         | 5.6mW/°C                                      |  |  |

- Absolute maximum ratings apply to both packaged parts and DICE, unless otherwise noted.

- For supply voltages less than ±22V, the absolute maximum input voltage is equal to the supply voltage.

## ELECTRICAL CHARACTERISTICS at $V_S = \pm 15 V$ , $T_A = 25 \, ^{\circ}$ C, unless otherwise noted.

|                                             |                        |                                                                                                       |                         | OP-77A                  |                      |                            | OP-77B                  |                      |                   |

|---------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|----------------------|----------------------------|-------------------------|----------------------|-------------------|

| PARAMETER                                   | SYMBOL                 | CONDITIONS                                                                                            | MIN                     | TYP                     | MAX                  | MIN                        | TYP                     | MAX                  | UNITE             |

| Input Offset Voltage                        | vos                    |                                                                                                       | _                       | 10                      | 25                   | -                          | 20                      | 60                   | \ير               |

| Long-Term Input Offset<br>Voltage Stability | ∆V <sub>OS</sub> /Time | (Note 1)                                                                                              | _                       | 0.2                     | -                    | -                          | 0.2                     | -                    | μV/Mo             |

| Input Offset Current                        | los                    |                                                                                                       | _                       | 0.1                     | 1.5                  |                            | 0.1                     | 2.8                  | nA                |

| Input Bias Current                          | i <sub>B</sub>         |                                                                                                       | -0.2                    | 1.2                     | 2.0                  | -0.2                       | 1,2                     | 2.8                  | nA                |

| Input Noise Voltage                         | ● <sub>np-p</sub>      | 0.1Hz to 10Hz (Note 2)                                                                                | _                       | 0.35                    | 0.6                  | _                          | 0.35                    | 0.6                  | #V <sub>p−p</sub> |

| Input Noise Voltage Density                 | • <sub>n</sub>         | f <sub>O</sub> = 10Hz (Note 2)<br>f <sub>O</sub> = 100Hz (Note 2)<br>f <sub>O</sub> = 1000Hz (Note 2) | _                       | 10.3<br>10.0<br>9.6     | 18.0<br>13.0<br>11.0 | =                          | 10.3<br>10.0<br>9.6     | 18.0<br>13.0<br>11.0 | nV/√Hz            |

| Input Noise Current                         | i <sub>np-p</sub>      | 0.1Hz to 10Hz (Note 2)                                                                                |                         | 14                      | 30                   |                            | 14                      | 30                   | рА <sub>р-р</sub> |

| Input Noise Current Density                 | in                     | f <sub>O</sub> = 10Hz (Note 2)<br>f <sub>O</sub> = 100Hz (Note 2)<br>f <sub>O</sub> = 1000Hz (Note 2) | =                       | 0.32<br>0.14<br>0.12    | 0.80<br>0.23<br>0.17 | =                          | 0.32<br>0.14<br>0.12    | 0.80<br>0.23<br>0.17 | pA√Hz             |

| Input Resistance —<br>Differential-Mode     | R <sub>IN</sub>        | (Note 3)                                                                                              | 26                      | 45                      | -                    | 18.5                       | 45                      | -                    | MΩ                |

| Input Resistance —<br>Common-Mode           | RINCM                  |                                                                                                       | -                       | 200                     | -                    | _                          | 200                     | _                    | Gn                |

| Input Voltage Range                         | IVR                    |                                                                                                       | ±13                     | ±14                     | _                    | ±13                        | ±14                     | _                    | ٧                 |

| Common-Mode Rejection Ratio                 | CMRR                   | V <sub>CM</sub> = ±13V                                                                                | _                       | 0.1                     | 1.0                  | _                          | 0.1                     | 1.6                  | ٧/٧ير             |

| Power Supply Rejection Ratio                | PSRR                   | V <sub>S</sub> = ±3V to ±18V                                                                          |                         | 1.0                     | 3                    | _                          | 1.0                     | 3                    | µV/∨              |

| Large-Signal Voltage Gain                   | Avo                    | $R_L \ge 2k\Omega$ , $V_O = \pm 10V$                                                                  | 5000                    | 12000                   |                      | 2000                       | 8000                    | _                    | V/mV              |

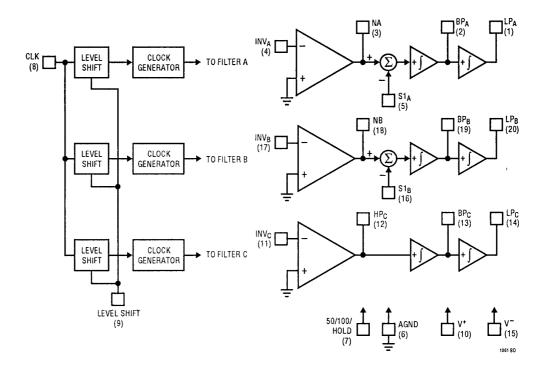

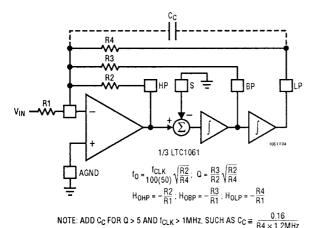

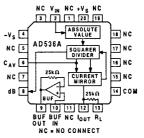

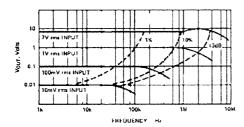

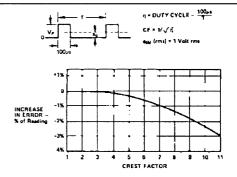

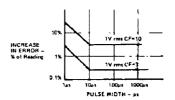

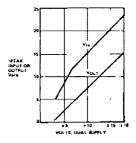

| Output Voltage Swing                        | v <sub>o</sub>         | R <sub>L</sub> ≥ 10kΩ<br>R <sub>L</sub> ≥ 2kΩ<br>R <sub>L</sub> ≥ 1kΩ                                 | ±13.5<br>±12.5<br>±12.0 | ±14.0<br>±13.0<br>±12.5 | <u>-</u>             | ± 13.5<br>± 12.5<br>± 12.0 | ±14.0<br>±13.0<br>±12.5 | <u>-</u>             | ٧                 |